Simulink Design Verifier uses formal methods to identify hidden design errors in models. It detects blocks in the model that result in integer overflow, dead logic, array access violations, and division by zero. It can formally verify that the design meets functional requirements. For each design error or requirements violation, it generates a simulation test case for debugging.

Simulink Design Verifier generates test cases for model coverage and custom objectives to extend existing requirements-based test cases. These test cases drive your model to satisfy condition, decision, modified condition/decision (MCDC), and custom coverage objectives. In addition to coverage objectives, you can specify custom test objectives to automatically generate requirements-based test cases.

Support for industry standards is available through IEC Certification Kit (for ISO 26262 and IEC 61508) and DO Qualification Kit (for DO-178 and DO-254).

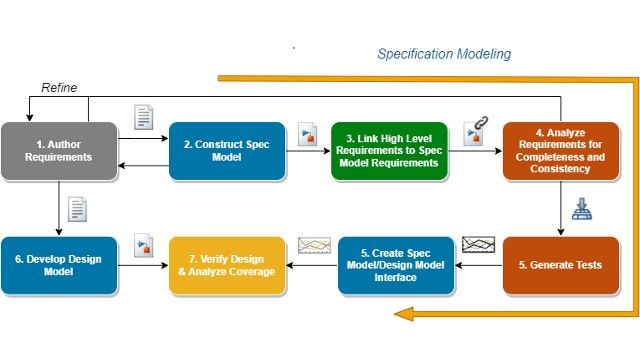

Validate Requirements

Check modeled requirements for consistency and completeness before beginning your design.

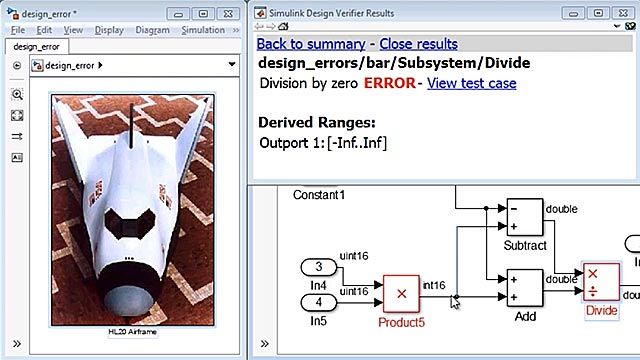

Detect Run-Time and Diagnostic Errors

Before you run simulations, you can detect run-time and modeling errors, including integer overflow, division by zero, array out of bounds, subnormal values, and floating-point errors as well as data validity errors.

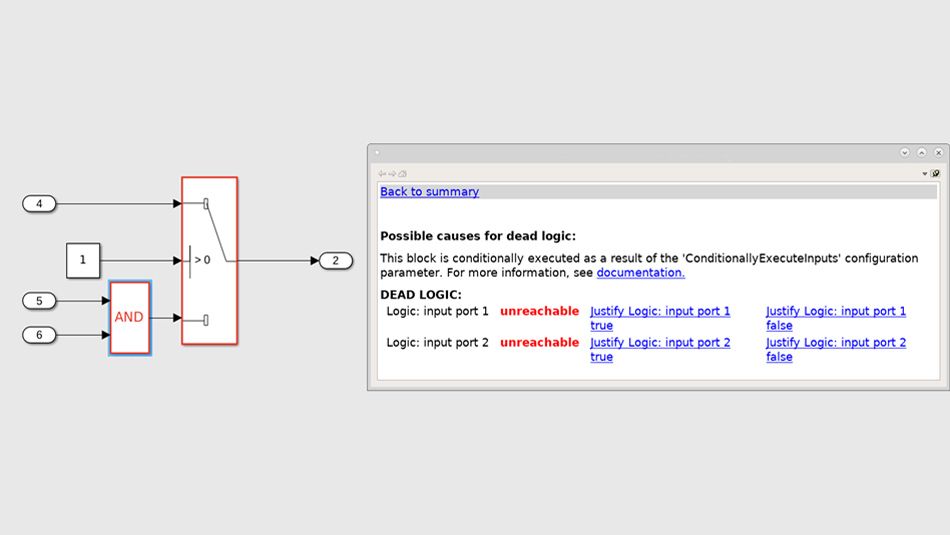

Find Dead Logic

Find objects in your model that cannot be activated during simulation and execution of generated code.

Analyze Missing Test Coverage

Augment and extend existing manually created test cases to address incomplete model coverage and coverage of generated code and C/C++ code called from Simulink blocks and in Stateflow charts.

Verify Formal Safety Requirements

Verify that your design behaves according to formally defined safety requirements (3:53) that you express using MATLAB, Simulink, and Stateflow.

Create Requirements-Based Test Cases

Generate test cases from models of system requirements.

Product Resources:

“By enabling us to analyze requirements quickly, reuse designs from previous products, and eliminate manual coding errors, Model-Based Design has reduced development times and enabled us to shorten schedules to meet the needs of our customers.”

MyoungSuk Ko, LS Automotive