## MATLAB EXPO 2016

Ein Modell - viele Zielsysteme

Automatische Codegenerierung aus MATLAB und Simulink

Dr.-Ing. Daniel Weida

• Structured

Text

#### **Industry trends**

**Code generation is expanding rapidly**

**Code generation offers many benefits**

Hardware resources need optimization

[in(Fail.One)

Warmup

VHDL

• Verilog

С

$\bullet$

## Agenda

Multi-target Production Code Generation

Hardware targets

**Continuous Verification and Validation**

Summary

## Agenda

Multi-target Production Code Generation

Hardware targets

**Continuous Verification and Validation**

Summary

#### Iveco Develops a Shift Range Inhibitor System for Mechanical 9- and 16-Speed Transmissions in Six Weeks

#### Challenge

Develop and deliver an automotive transmission management system in six weeks

#### **Solution**

Use Model-Based Design to model, implement, test, and deploy the management system on a PLC

#### **Results**

- Development time cut by 40%

- Specification and implementation errors eliminated

- PLC design reused on a microprocessor

An Iveco heavy-duty vehicle.

"Our system engineers work directly with our software engineers on the Simulink model. This speeds development because there is no misinterpretation of requirements. When we're confident that the model is right, we save even more time by generating code from it, with no implementation errors."

> Demetrio Cortese Iveco

## **Multi-target challenges**

**Model-Based Design**

- How do I size the motors?

- Can I get desired performance?

- Does my system work if component values change?

#### **Multi-target Production Code Generation**

- How do I size the processing hardware?

- Can I get desired execution speed?

- Does the system work if component cores change (e.g., PLC to DSP)?

"After implementing the PLC version with Simulink PLC Coder, we reused the model, with few modifications, and generated the microprocessor code using Embedded Coder. We switched from a structured text implementation to C, just by changing the code generation product we used."

## Agenda

Multi-target Production Code Generation

#### Hardware targets

**Continuous Verification and Validation**

#### Summary

📣 MathWorks

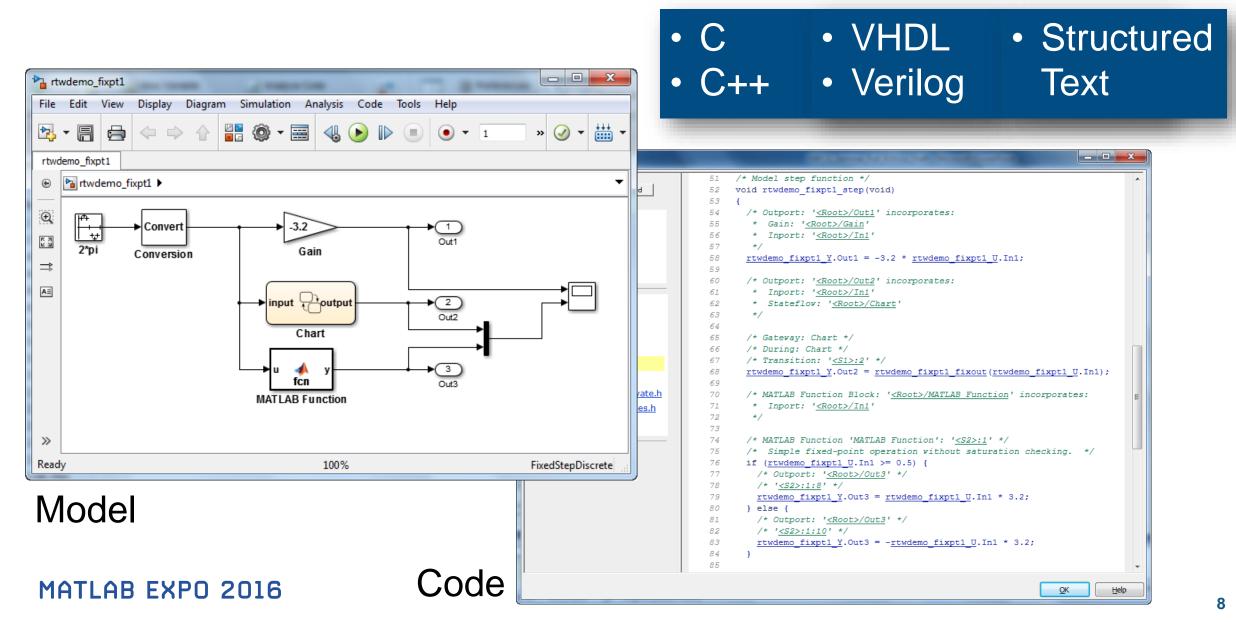

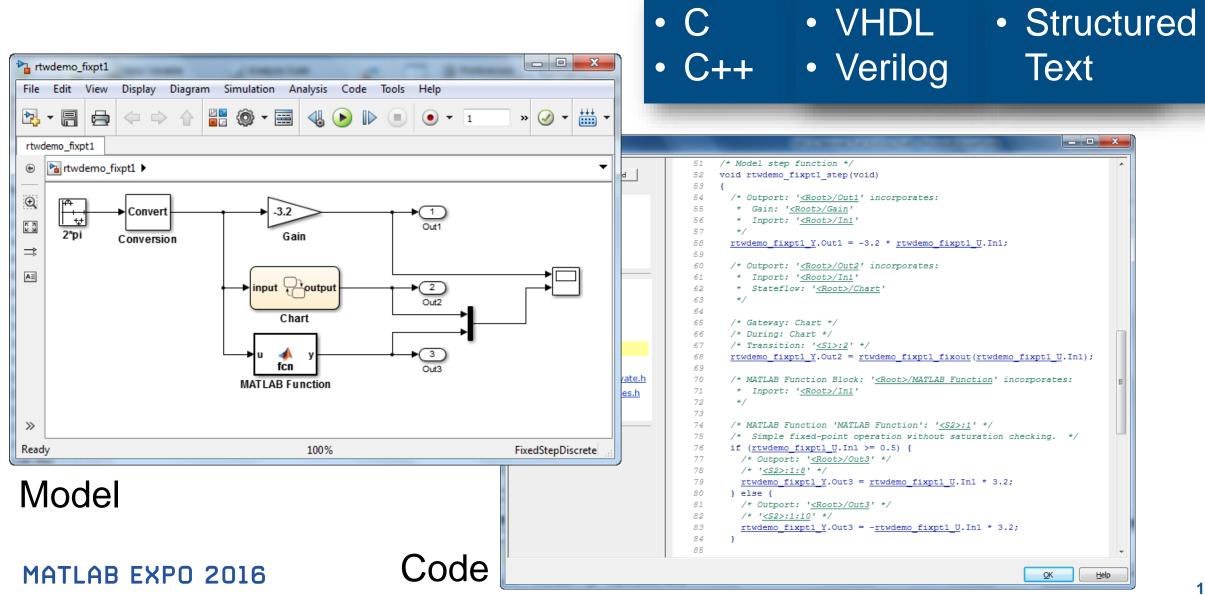

## **Code Generation: <u>Five</u> languages**

#### **Structured Text**

## C/C++

## **VHDL/Verilog**

MathWorks<sup>®</sup>

## **Code Generation: Five languages**

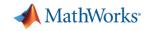

## Hardware Support: <u>Any</u> device

- Any device with portable code for algorithm code generation

- Coder support packages offer device-specific system executable generation

- ARM ... C2000 ... Zynq

- Hardware vendors offer their own support packages

- Freescale, Infineon, Microchip, Renesas, TI, STMicroelectronics,

## **Hardware Constraints**

A MathWorks<sup>®</sup>

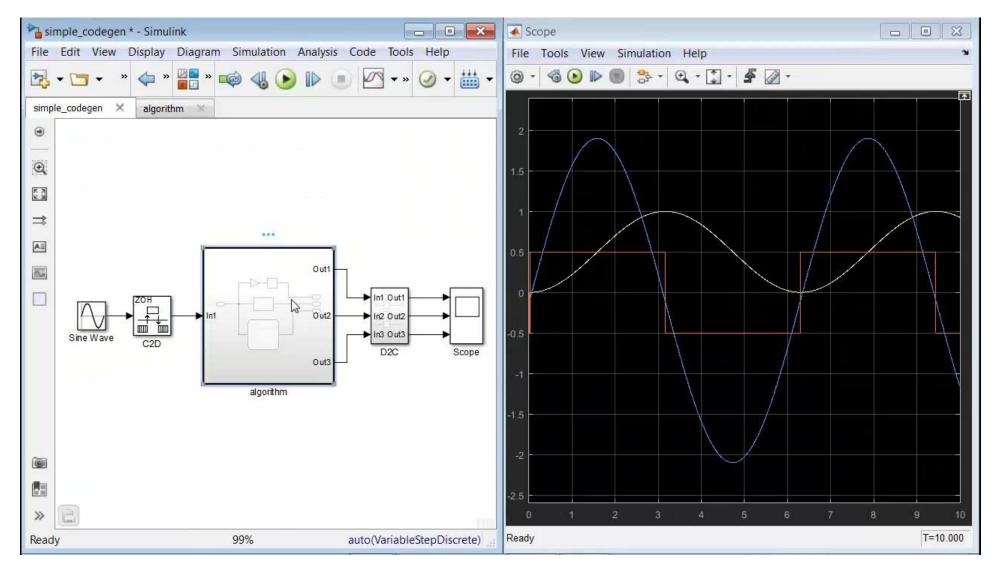

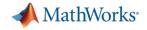

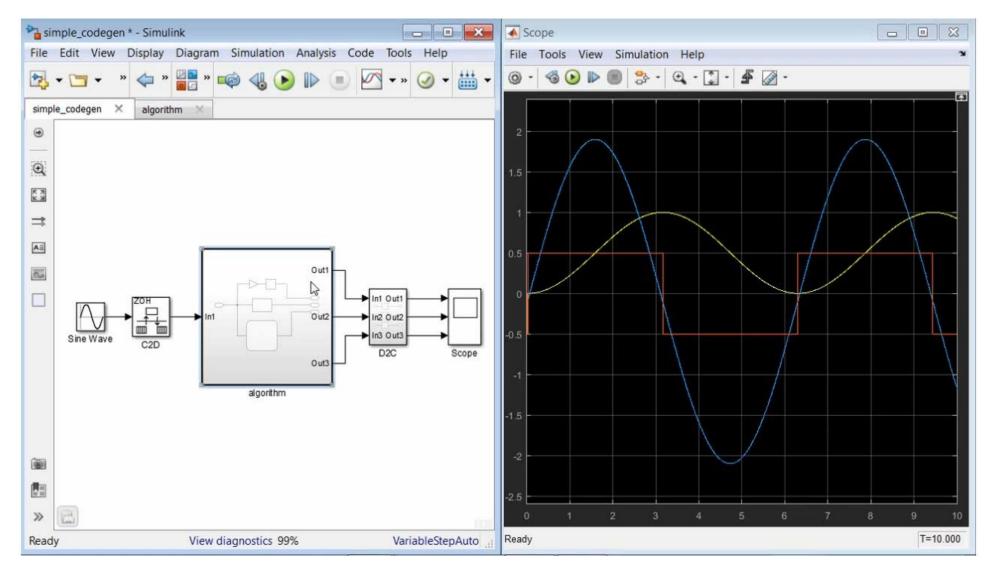

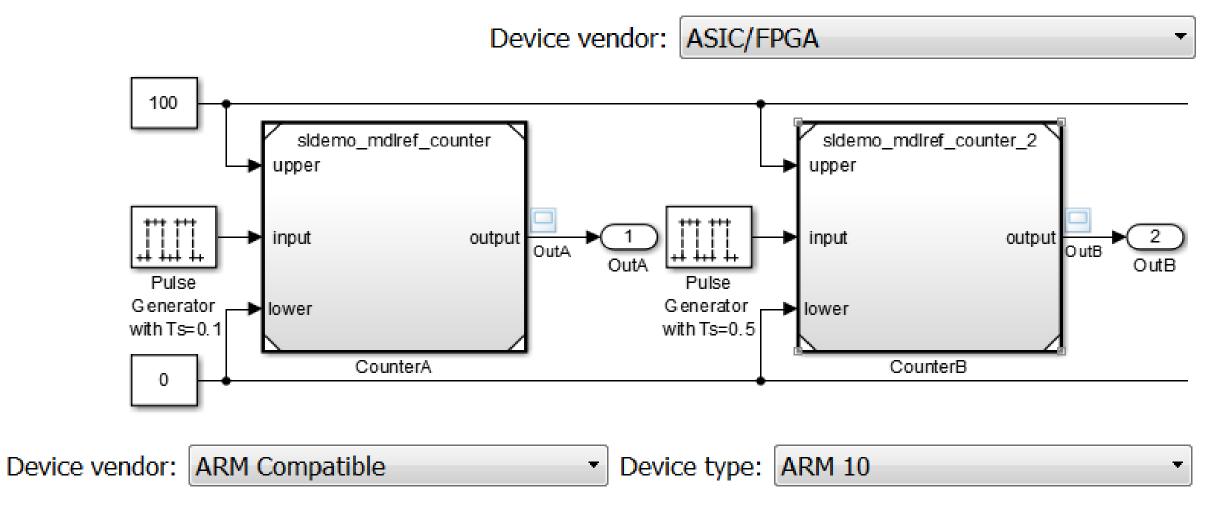

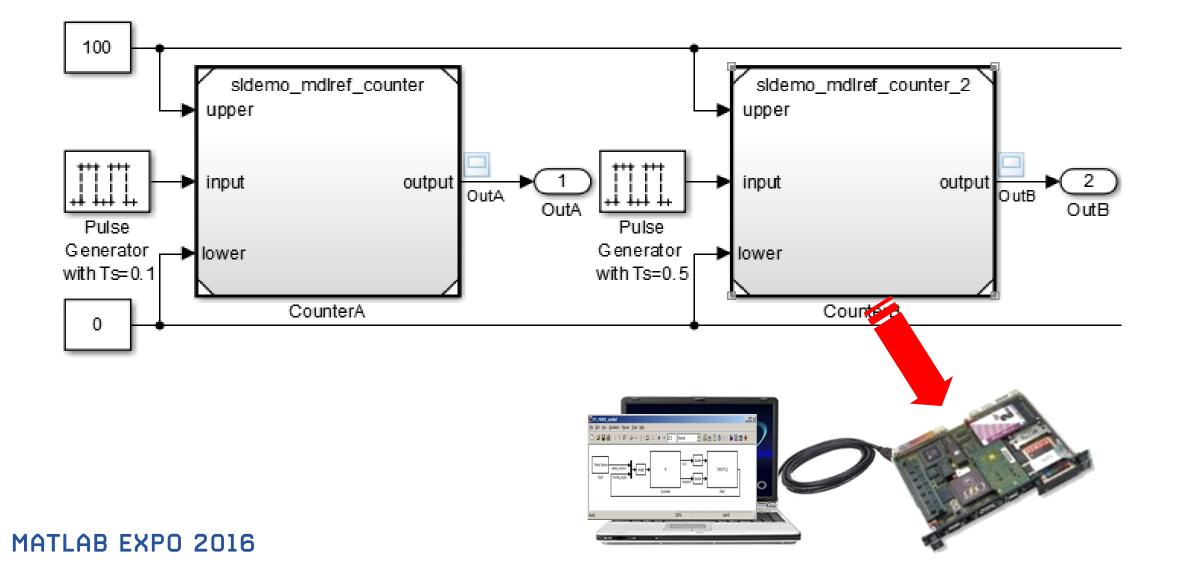

## **Simulation for Mixed Targets**

## Agenda

Multi-target Production Code Generation

Hardware targets

#### **Continuous Verification and Validation**

Summary

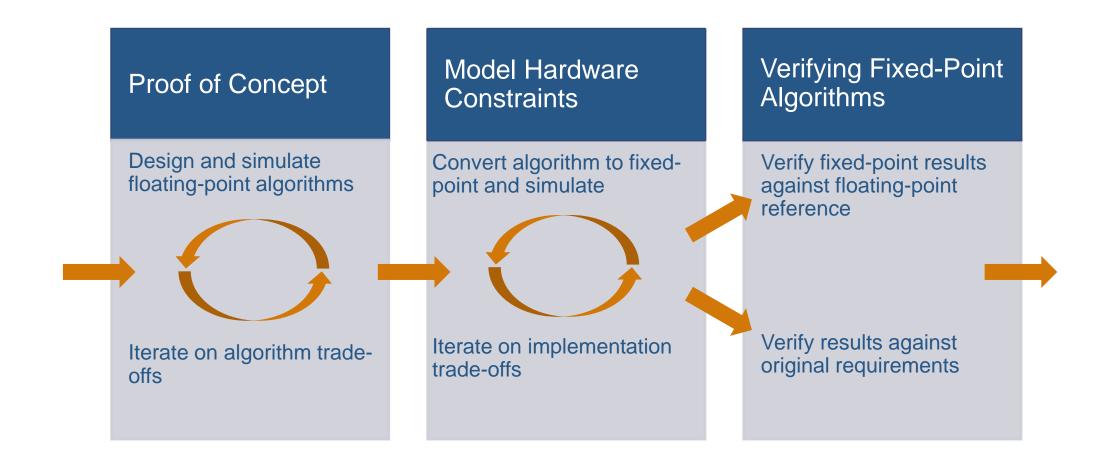

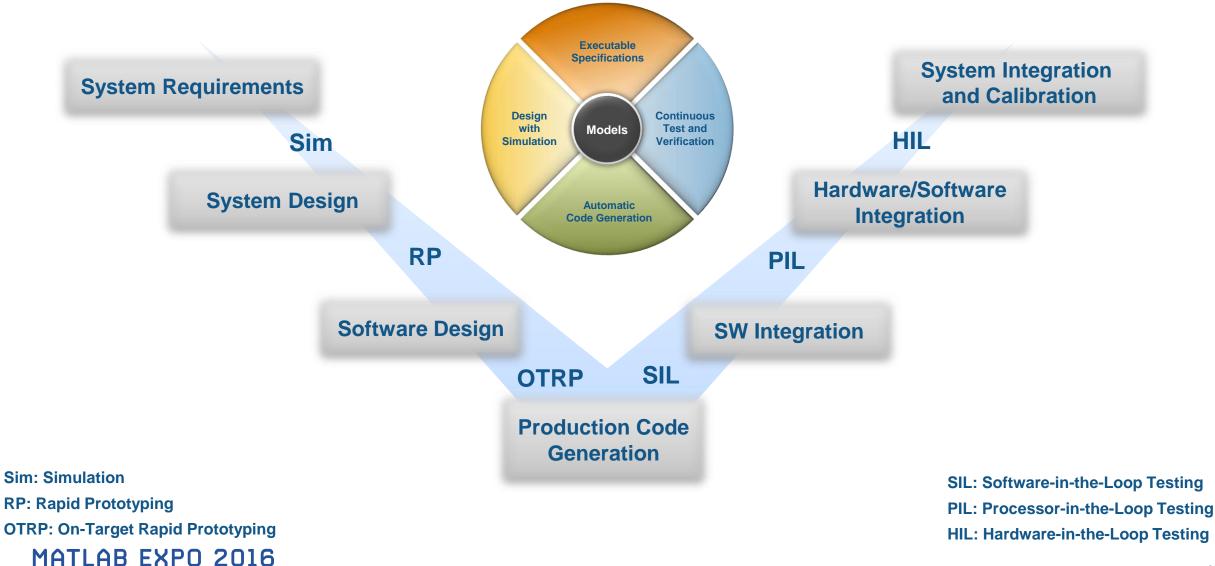

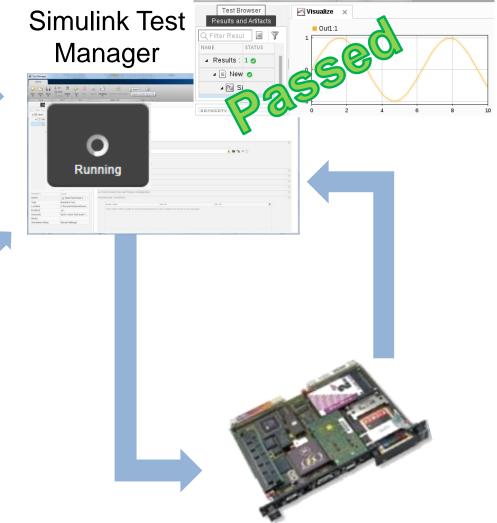

## **Embedded System Development Process**

#### with Model-Based Design

**Rapid Prototyping**

MATLAB EXPO 2016

MathWorks<sup>®</sup>

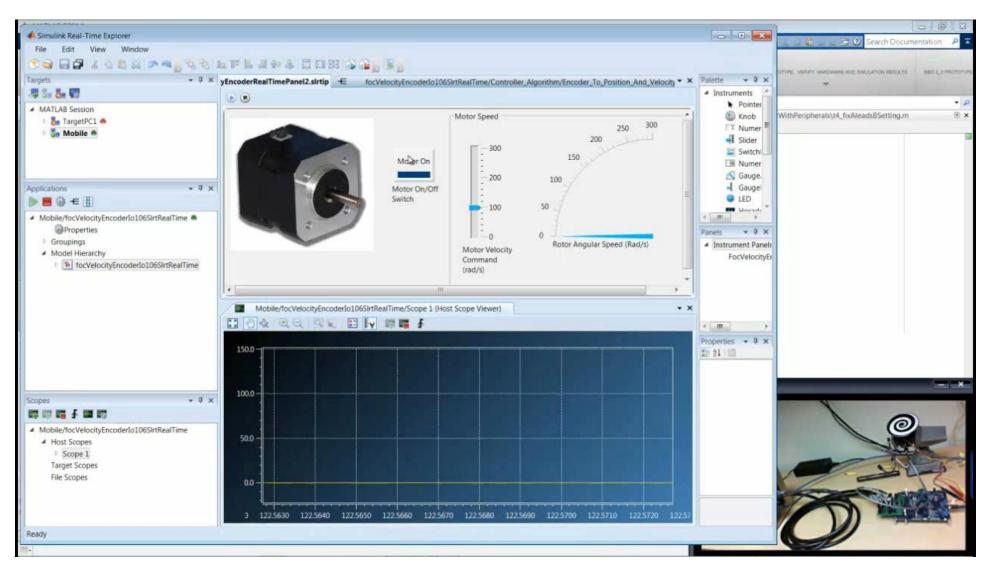

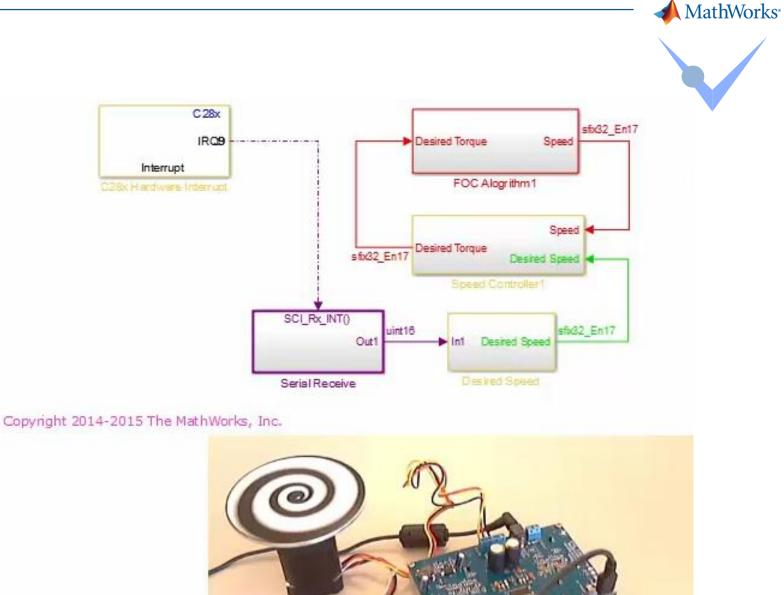

## **On-Target Prototyping**

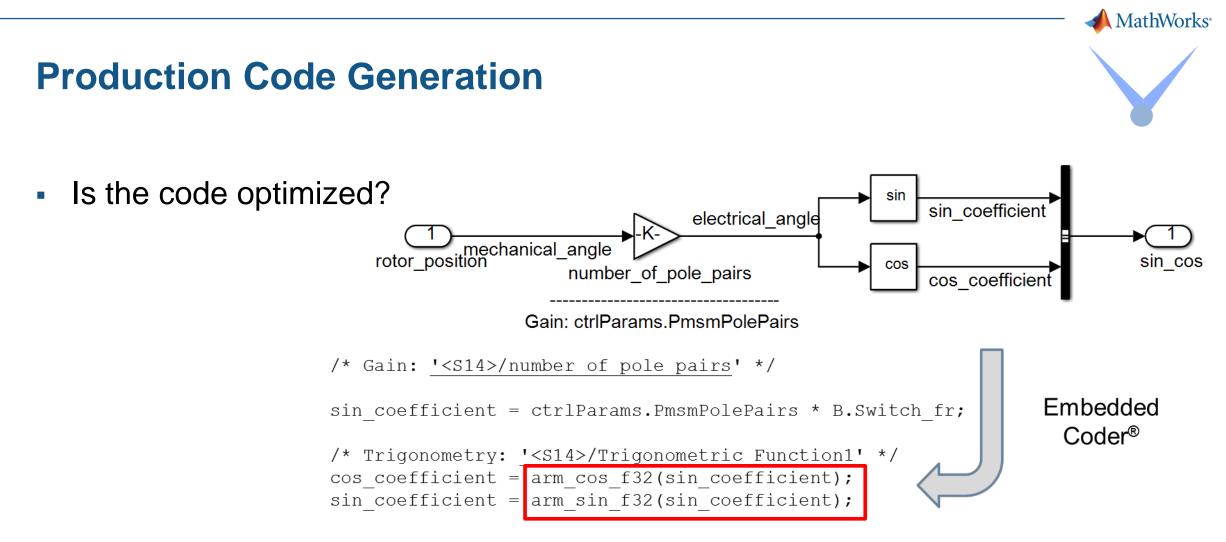

Does algorithm perform well on actual device with true latencies?

- Code Replacement Tables

- Use of e.g. CMSIS library for code optimization for ARM

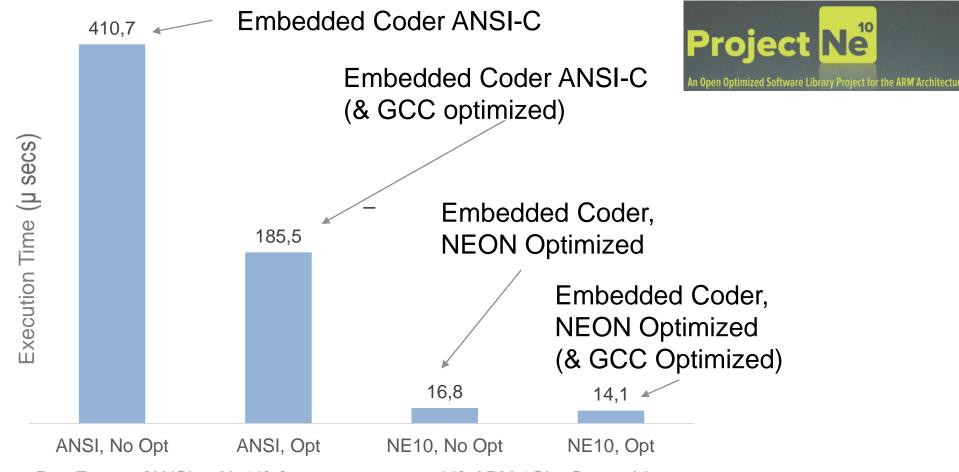

## **Results for ARM Cortex-A**

Run Format: [ANSI or Ne10], [gcc no opt or gcc -02], ARM 1Ghz Cortex A8

#### **Processor-in-the-loop**

## **Target requirement-based testing**

Simulink model

Hardware specific model

# Simulation Test Harnesses

Hardware Test Harnesses

## **Coding Standards**

#### **MISRA-C**

|                                           | del Advisor - systemModel<br>Edit Run Settings | -                | Help        |                               |                   |        |

|-------------------------------------------|------------------------------------------------|------------------|-------------|-------------------------------|-------------------|--------|

|                                           | > 🗟 😓 📼 Find:                                  |                  |             | $\Leftrightarrow \Rightarrow$ |                   |        |

|                                           |                                                |                  |             |                               |                   |        |

|                                           | odel Advisor                                   |                  |             |                               |                   |        |

|                                           | By Task                                        |                  |             |                               |                   |        |

|                                           | Dy Rusk Dy Rusk Code Gene                      | ration Efficienc | v           |                               |                   |        |

|                                           | Data Trans                                     |                  | ,           |                               |                   |        |

|                                           | E E Frequency                                  |                  | nation      |                               |                   |        |

|                                           | 🖻 🔳 🗀 Managing [                               | Data Store Men   | nory Bloc   | ks                            |                   |        |

| 🖻 🖉 🗀 Managing Library Links And Variants |                                                |                  |             |                               |                   |        |

|                                           | 🖻 🔲 🍋 Migrating te                             |                  | tializatior | n mode                        |                   |        |

|                                           | 🕨 🔳 🛅 Model Metr                               |                  |             |                               |                   |        |

|                                           | Model Reference                                |                  |             | 010                           |                   |        |

|                                           | ▲ ☑                                            | onfiguration pa  |             |                               | 012               |        |

|                                           |                                                | r blocks not re  |             |                               |                   |        |

|                                           |                                                | r unsupported    |             |                               | 0.2012            |        |

|                                           |                                                | sage of Assignr  |             |                               |                   |        |

|                                           |                                                | for bitwise ope  |             |                               | ers               |        |

|                                           | 🗹 💷 ^Check                                     | for recursive fu | inction ca  | lls                           |                   |        |

|                                           | 🗹 💷 ^Check                                     | for equality an  | d inequal   | ity operations                | on floating-point | values |

|                                           |                                                | for switch case  |             | ons without a                 | default case      |        |

|                                           | Nodeling P                                     | hysical System   |             |                               |                   |        |

| û ∐n                                      | ograde Advisor                                 |                  |             |                               |                   |        |

| _                                         |                                                |                  |             |                               |                   |        |

| lá Co                                     | ode Generation Advis                           | sor              |             |                               |                   |        |

| 🕜 Pe                                      | rformance Advisor                              |                  |             |                               |                   |        |

#### **STARC HDL**

| General                                | Ports                                      | Optimization       | Coding style             | Coding standards | Diagr |  |  |

|----------------------------------------|--------------------------------------------|--------------------|--------------------------|------------------|-------|--|--|

| Choose coding standard                 |                                            |                    |                          |                  |       |  |  |

| HDL coding standard: Industry -        |                                            |                    |                          |                  |       |  |  |

| Report op                              | tions                                      |                    |                          |                  |       |  |  |

| 🔲 Do not                               | show pa                                    | ssing rules in coo | ling standard rep        | port             |       |  |  |

| -Basic cod                             | ing rules                                  |                    |                          |                  |       |  |  |

| Check                                  | Check for duplicate names                  |                    |                          |                  |       |  |  |

| Check for HDL keywords in design names |                                            |                    |                          |                  |       |  |  |

| Check                                  | Check module, instance, entity name length |                    |                          |                  |       |  |  |

| Minim                                  | um 2                                       |                    |                          |                  |       |  |  |

| Maxin                                  |                                            |                    | and a state of the state |                  | ~     |  |  |

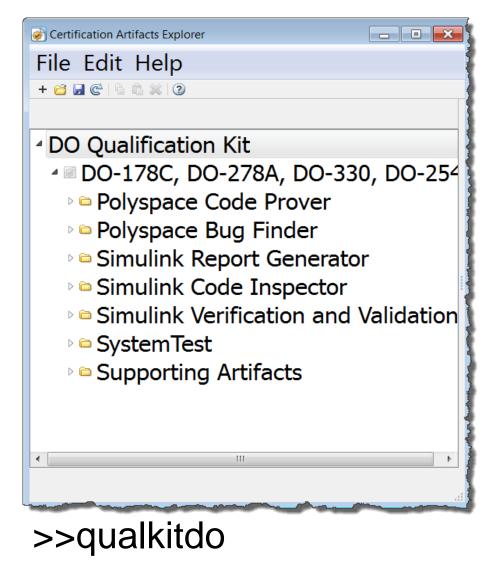

## **DO Qualification Kit**

## **IEC/ISO Certification Kit**

Certification Artifacts Explorer

| File Edit Help                            |

|-------------------------------------------|

| + 🖆 🖬 🤄 🖣 🖏 🛛 🕐                           |

|                                           |

| IEC Certification Kit                     |

| 🖌 🔤 ISO 26262, IEC 61508, EN 50128, IEC 6 |

| 🖻 🖻 Embedded Coder                        |

| 🖻 🖻 Polyspace Bug Finder                  |

| 🖻 🖻 Polyspace Code Prover                 |

| 🖻 🖻 Simulink Design Verifier              |

| Simulink Verification and Validation      |

| 🖻 🖻 Simulink PLC Coder                    |

| 🖻 🖻 Supporting Artifacts                  |

|                                           |

|                                           |

|                                           |

|                                           |

| >>certkitiec                              |

## **Model-Based Design – Certification Examples**

Honeywell Aerospace USA Flight Control Systems

TRW Germany Electronic parking brake control system

Weinmann Medical Germany Transport ventilator

Alstom Grid UK HDVC Power Systems

Airbus Helicopters Certified flight software

Alstom France Train Control Systems

## Agenda

Multi-target Production Code Generation

Hardware targets

**Continuous Verification and Validation**

#### Summary

• Structured

Text

## **Key Take-Aways**

**Code generation is expanding rapidly**

**Code generation offers many benefits**

Hardware resources need optimization

[in(Fail.One)

Warmup

VHDL

• Verilog

$\bullet$