# From High-Level Algorithms to ASML Automated Digital Design Flows

John van Tol Competence Leader Embedded Logic and Firmware (ELF) Development

May 21<sup>st</sup>, 2019 - Eindhoven

Public

# Key Takeaways

- **Public** Slide 2 11-03-2019

- 1. ASML business drivers: Quality and Time-to-Market, require an efficient workflow for getting smart algorithms into high speed digital hardware (FPGAs)

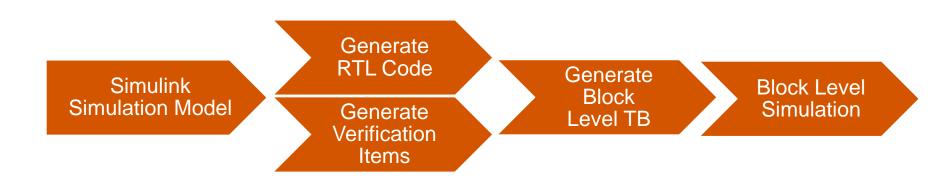

- 2. Adoption of Model-Based Design into the ASML Digital Design Flow achieves this with automatic generation of HDL source code and test bench code

- 3. Model-Based Design reduces the gap between system architect and design engineer

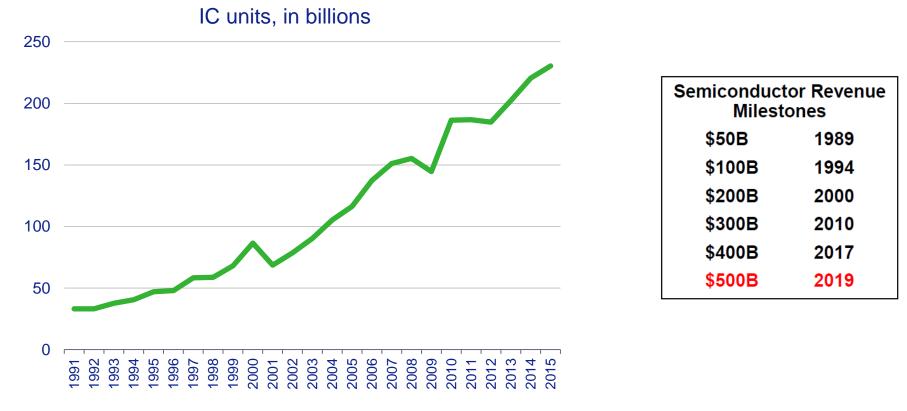

## Chips are everywhere!

In 2015, 230 billion ICs were made, 30 for every man, woman and child on the planet

**Public** Slide 3 07-04-2018

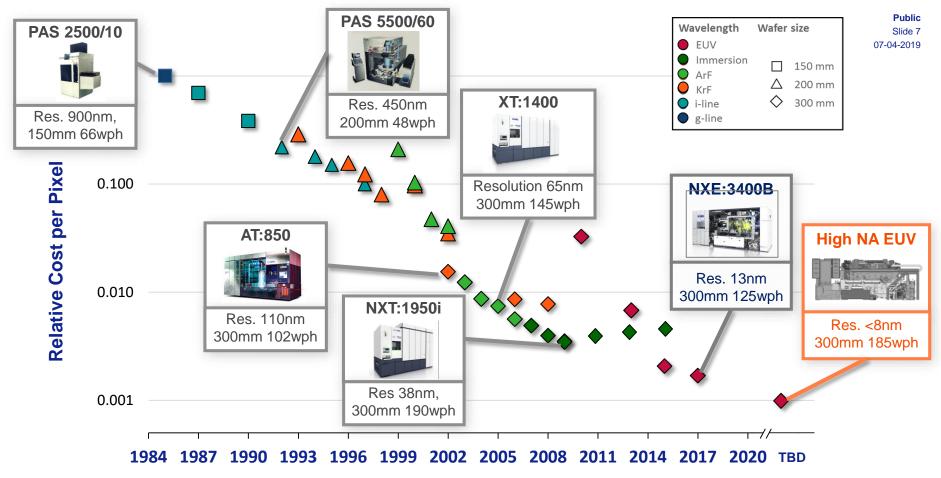

#### We develop and build lithography systems for manufacturing those IC's

150 tons of precision equipment

works with single nano-meter precision: Grass grows at a speed of 33 nano-meter per second

Public

Slide 4

## Moore's Law means doing "More with Less"

1000 \$, 512 MB + GB flash, 200 g,< 1W

Public Slide 5 07-04-2019

30M\$, 8 Mb, 5500 kg, 150 kW

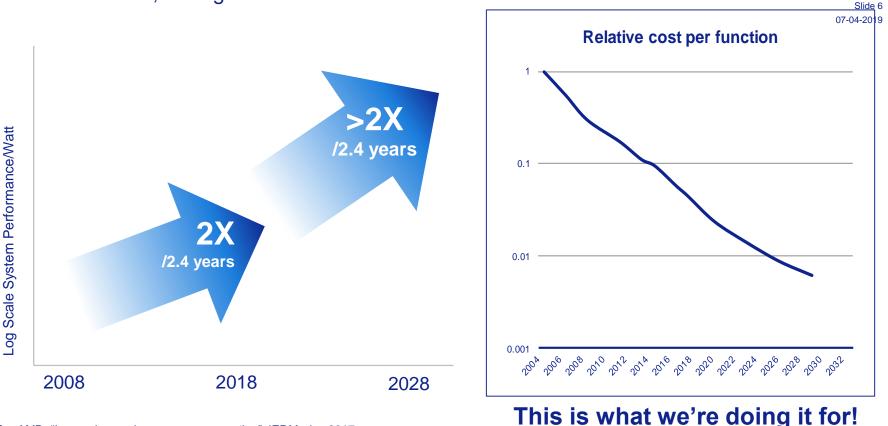

# The industry is driven by Moore's law,

which continues, through ideas and value creation

<sup>1</sup>Lisa Su, AMD, "Immersive era in consumer computing", IEDM, dec 2017

<sup>2</sup>Gordon Moore, "Progress in digital integrated Electronics" International; Electronic Device Meeting,, IEEE, 1975, p p 11-13 ASML Market Research Public

#### Our systems enable the faster, better, cheaper chips of tomorrow

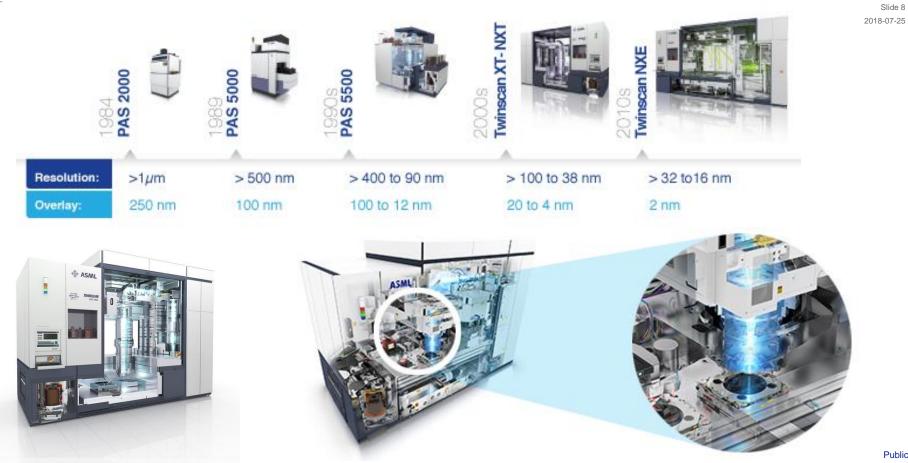

# ASML makes the machines for making IC's

**ASML**

Public Slide 8

Public Slide 9 2018-07-25

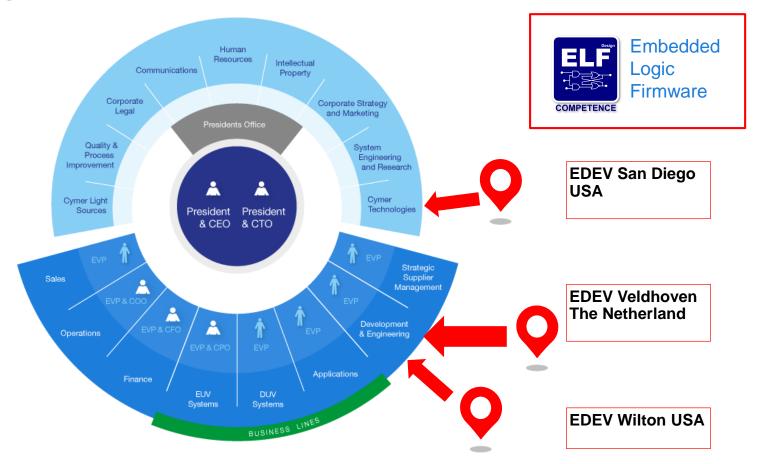

# Electronic Development within D&E ASML

Public

**ASML**

Slide 10 27-11-2018

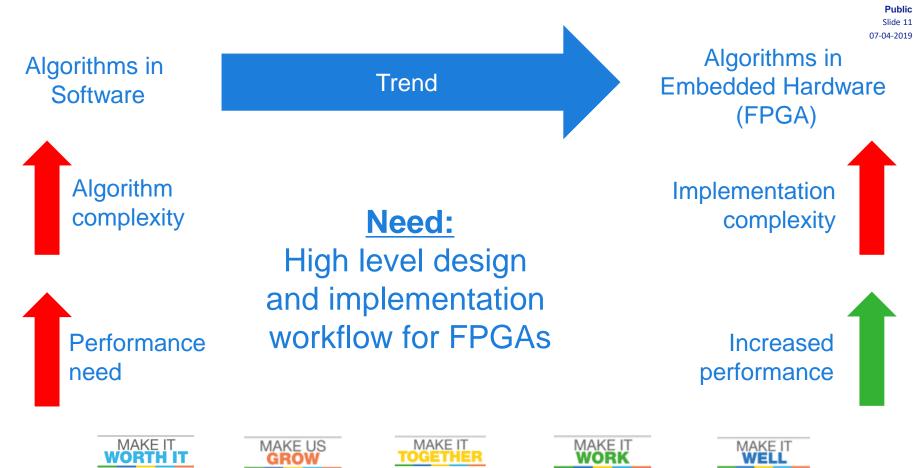

# **Goals and Challenges**

# Challenges

# 1. One ASML common method of developing algorithms in FPGAs

# 2. Make modeling, simulation and code generation accessible for ELF engineer

3. Reduce the gap between system architect and ELF engineer

**ASML**

Slide 13 27-11-2018

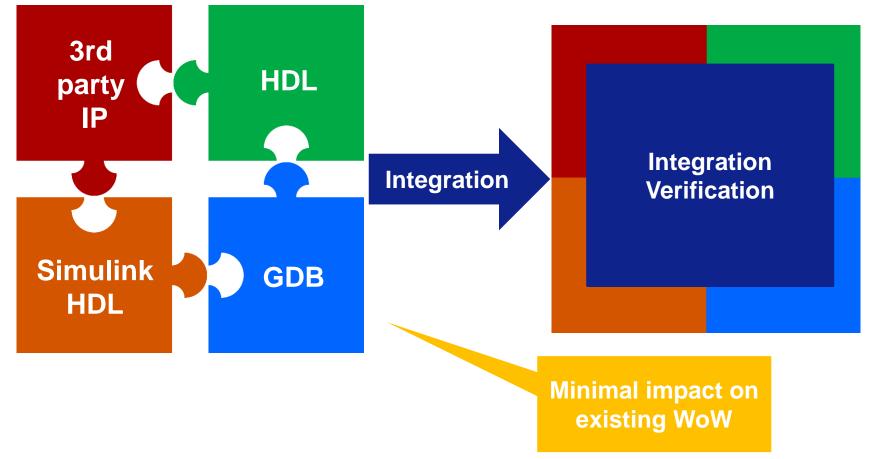

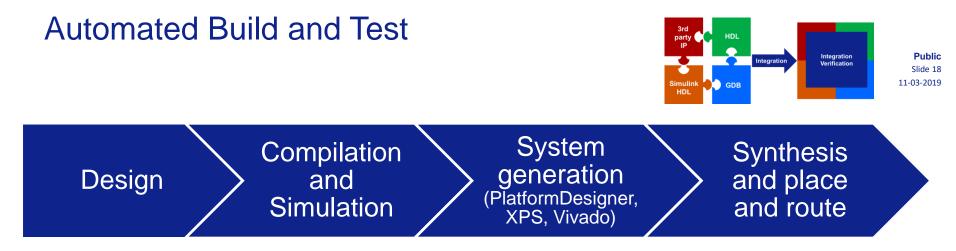

# How we do it

# ASML ELF Way-of-Working (WoW)

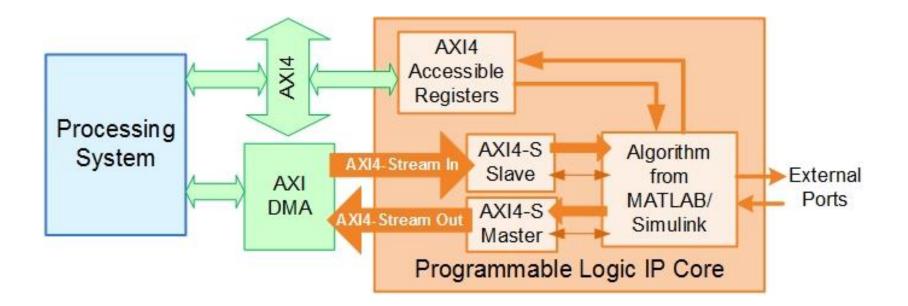

GDB = Generic Design Block, HDL = Hardware Description Language

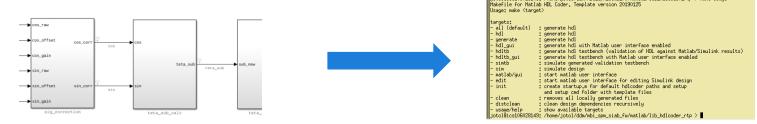

# ASML ELF Way-of-Working, elaborated

### ASML workflow to create algorithm subsystem, an example

1. Buildfiles are used to automate the various tasks involved in the FPGA design flow

2. The "Build process" makes extensive use of (GNU) Make

**ASML**

Slide 19 27-11-2018

# Achievements and Outlook

# Using HDL Coder in ELF projects

- Established workflow within the entire ASML organization.

- IT team (IT4E) maintains development software and Linux servers for any ELF project

- Standard use of HDL Code Generation in ELF Design Flow (DDM2/Buildfiles)

- Integrated with workflow for communication protocols (GDB), integration tool (QSYS/Platform designer/Vivado Block design), hardware interfaces (VHDL)

- Improved development of Digital Signal Processing (DSP) functions (vs. handwritten RTL and/or Testbench)

- Easier to make changes in a late stage of the project without compromising quality

- Especially suited for complex DSP functions

- Future work: automatic FPGA-In-the-Loop (FIL)

**Public** Slide 20 07-04-2019

# Key Takeaways

- **Public** Slide 21 11-03-2019

- 1. ASML business drivers: Quality and Time-to-Market, require an efficient workflow for getting smart algorithms into high speed digital hardware (FPGAs)

- 2. Adoption of Model-Based Design into the ASML Digital Design Flow achieves this with automatic generation of HDL source code and test bench code

- 3. Model-Based Design reduces the gap between system architect and design engineer