# High-Performance Semiconductors

Magnetic Sensor Integrated Circuits

Power Integrated Circuits

## Automotive ASIC Model Based Design

Jamie Haas Director of Design Engineering Advanced Sensor Technology Business Unit

**Allegro Confidential Information**

Allegro Confidential Information

### **Sensor Applications**

### • Automotive

- Steering

- Engine

- Transmission

- Hybrid/Electric Motor

- Seat Belt

- More!

- Consumer Applications

- Industrial Controls

- Current Sensing

An Overview of Allegro's MBD Success

\*\*\*\*\*\*\*\*\*\*\*

- We Started taking a serious look at Simulink MBD for ASIC Development in 2014

- □ Team Adoption hit the "knee" of the curve in 2015

- A total of 8 device digital control systems and signal paths auto generated from Simulink

- □ Interpolation engines

- Digital filters

- □ Signal Processing Algorithms

- Digital PLL's

- Digital Sigma Delta DAC's

- Silicon Evaluation has demonstrated ZERO bugs from auto generated code to date.

Allegro Confidential Information

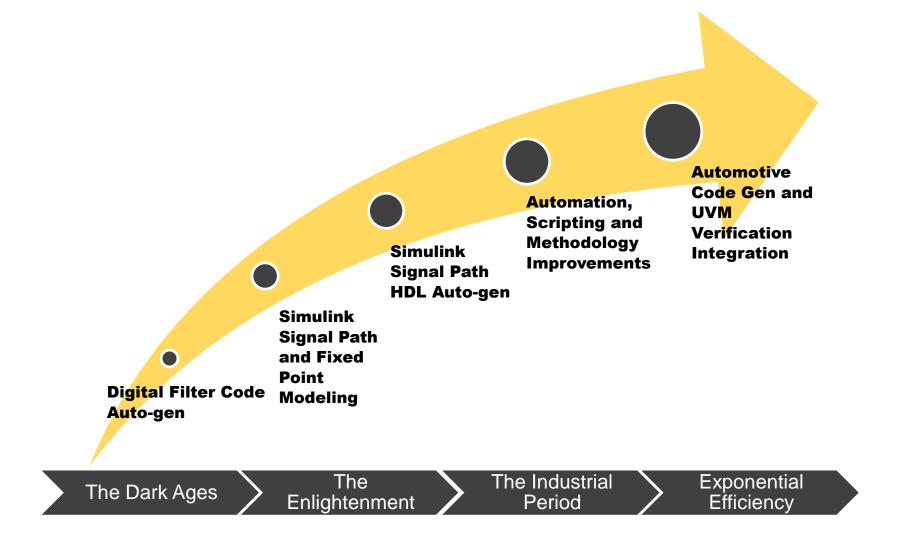

### The Evolution of Allegro's Model Based Design (MBD) Flow

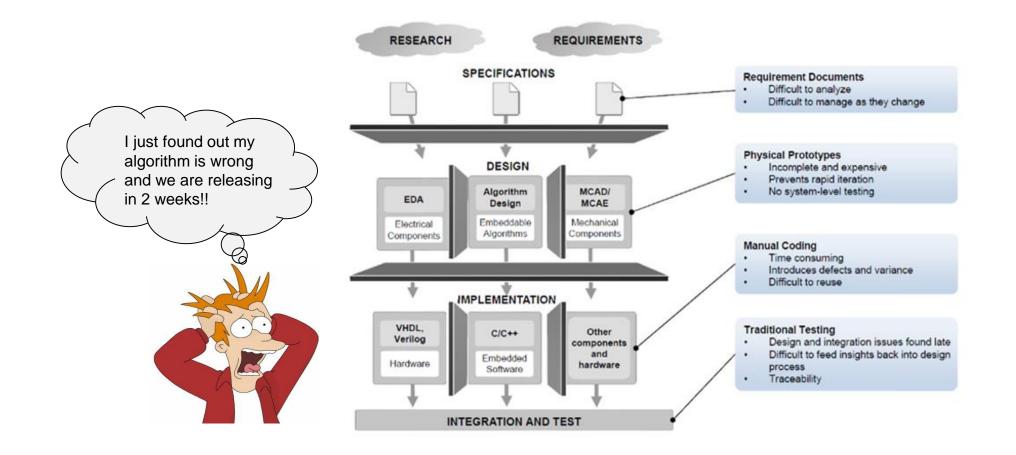

## "The Dark Ages" Traditional ASIC Design

Allegro Confidential Information

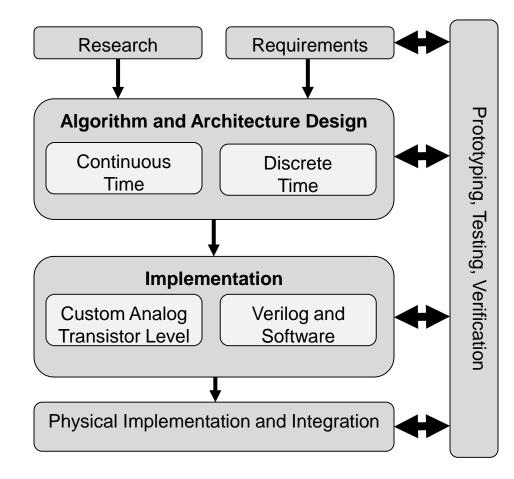

### The Enlightenment: Model Based Design

- Architecture and Algorithm

Design Evolve into Executable

Specifications

- Front load testing and verification

- Development is "parallelized"

- Continuous Equivalency Testing is utilized

- Image: And of course autogenerated production code

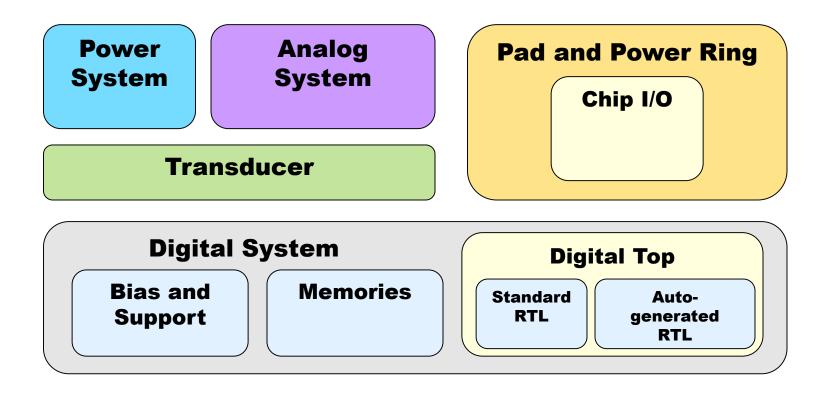

### **ASIC Sensor Components**

Allegro Confidential Information

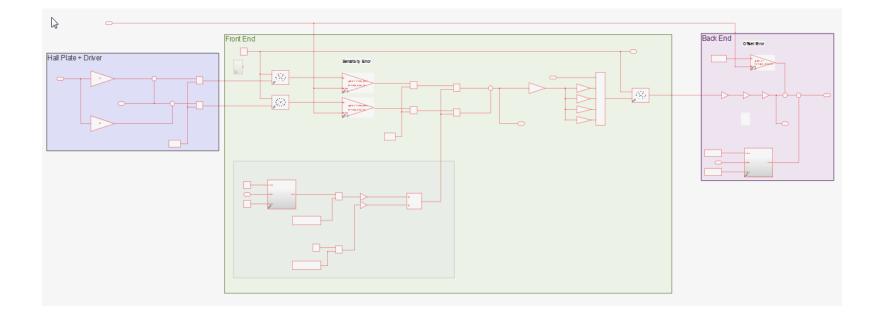

### Mixed Signal ASIC Components

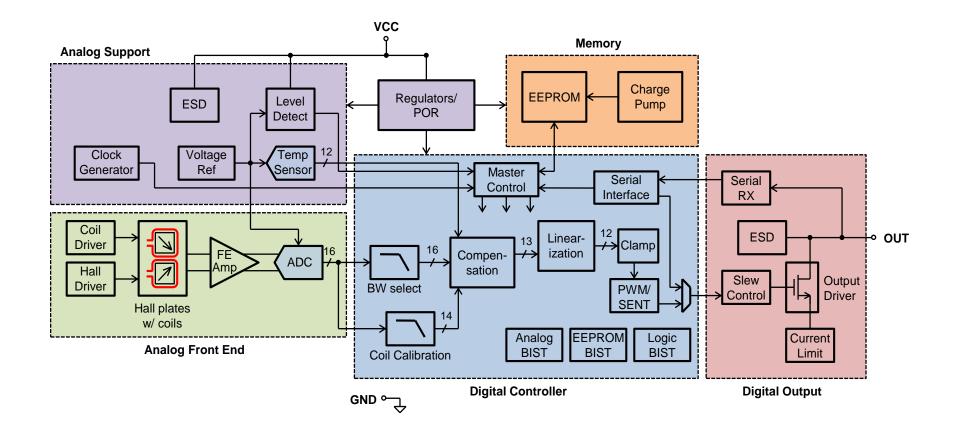

### **Precision Automotive Magnetic Sensor**

## **ASIC Sensor Simulink Modeling**

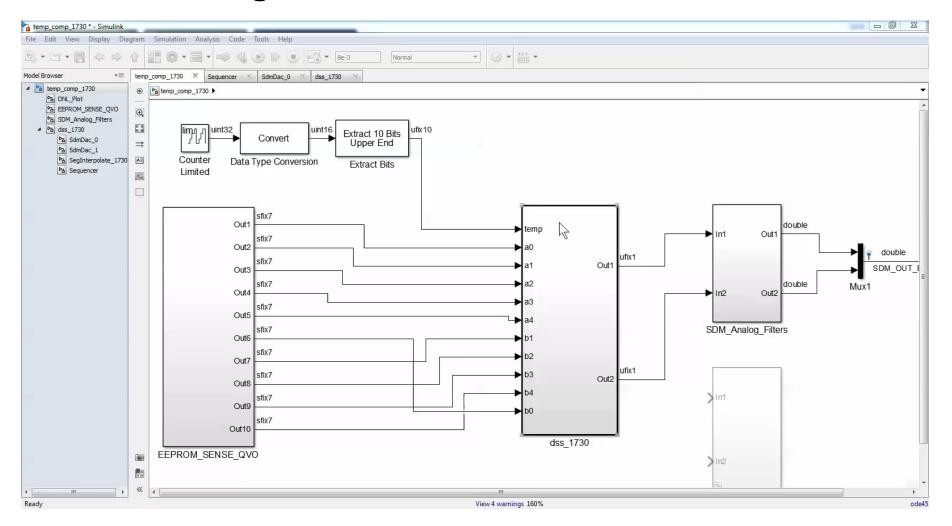

- How do we handle the memory (EEprom configuration)

- Simulink Model Types

Spec Model

HDL Gen: Stateflow

HDL Gen: Matlab Function

Validation Model

Allegro Confidential Information

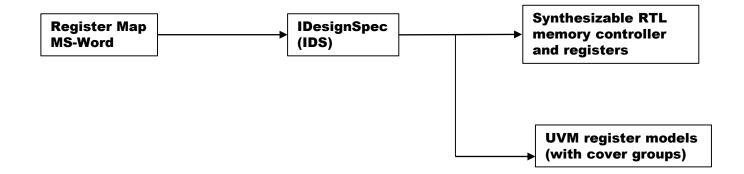

### **Memories: Automatic Register Generation**

- □ The Word based register map is the single point for documenting all registers

- **RTL** is generated using the Agnisys IDesignSpec tool

- Register models required by DV (Design Verification) are generated using the Agnisys IDesignSpec tool

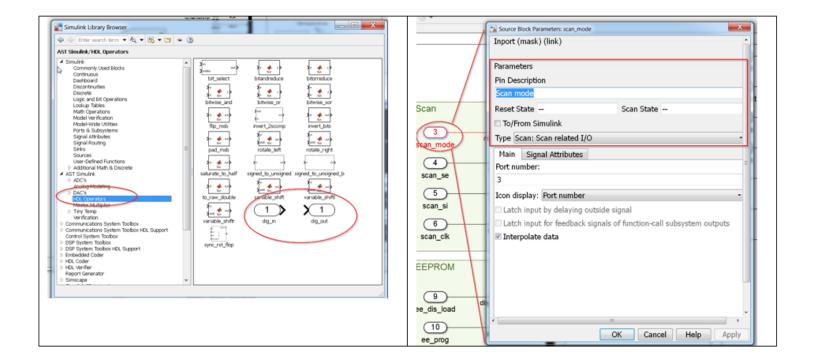

### Memories: Link Simulink Model to Memory Map

- **Custom Inports and Outports with attributes where created**

- Additional attributes are used by Matlab Report Generator for automated document generation

### **Simulink Spec Model**

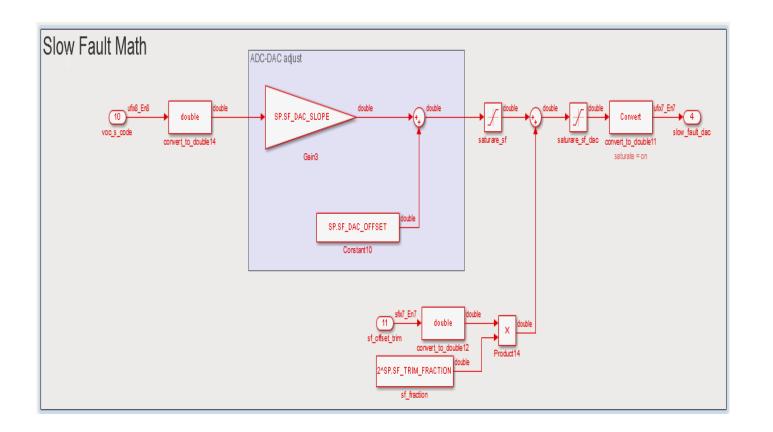

A Spec Model is the "golden model" of what you are trying to achieve.

- Easy to read

- □ Simple as possible

- Requirements are linked to the spec models

122222222222222

- **HDL** optimizations

- Keep data types as doubles where possible

- Using DPI-C , System Verilog models are created from the spec models

Allegro Confidential Information

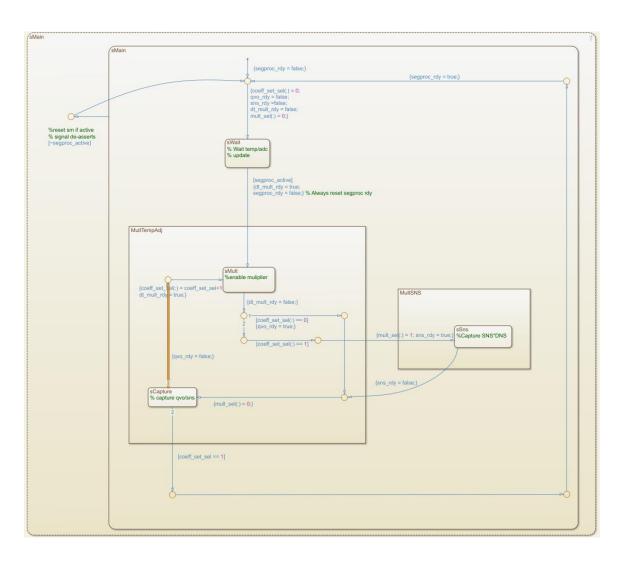

### **The Power of Stateflow**

- □ Stateflow is a universal tool

- Stateflow allows for efficient control logic design that is self documenting and translates to efficient RTL(\*\*)

- □ SAR ADC Controller

- Multiplier Sharing

- Stateflow can be used as a verification driver (handles asynch events)

- Stateflow can be used to model analog switched capacitor charge transfer!

- Stateflow charts can be embedded within Stateflow charts

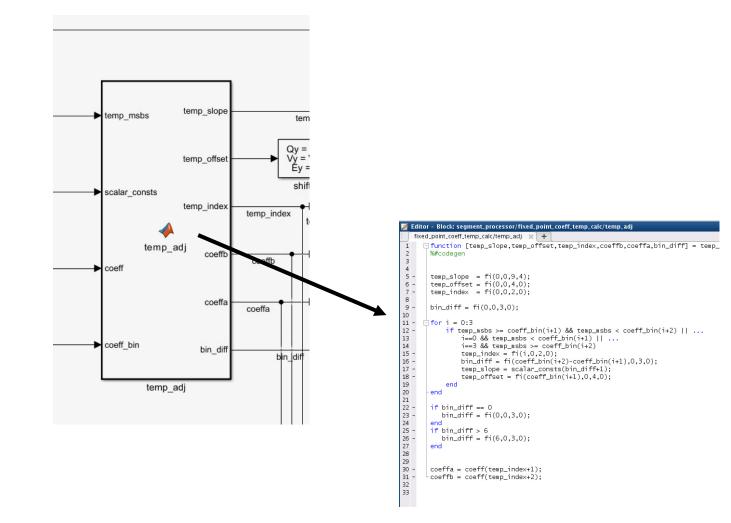

### **Flexibility of Matlab Function Block**

- Code generation is not limited to Simulink fixed point and Stateflow

- Many functions and operations are more efficiently written as a Matlab function

- Floating point functions

coder.approximate

- □ Simulink is your canvas

### **Simulink Validation Model**

- □ A validation model generates "evidence" that specific requirements are met

- □ Automated regressions require that a pass/fail criteria be used

- □ Asserts are your friend!

- □ We hope to see the asserts pass through to the auto generated HDL very soon!

# Simulink Code Generation for Digital (and Analog ?!)

Allegro Confidential Information

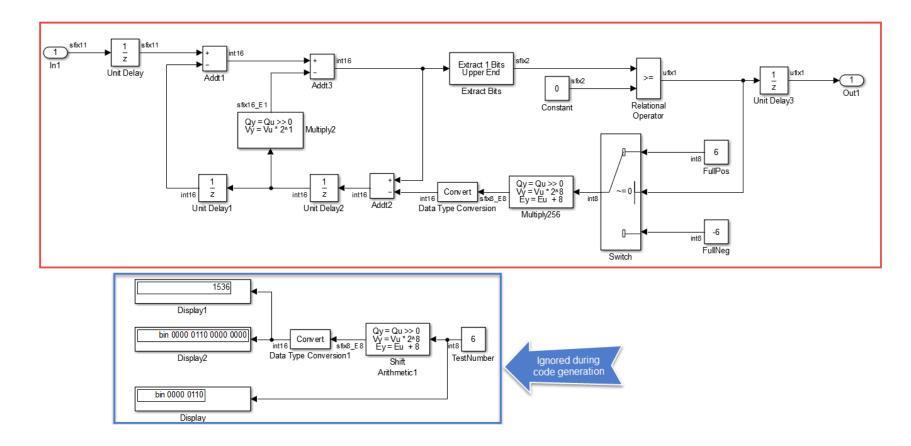

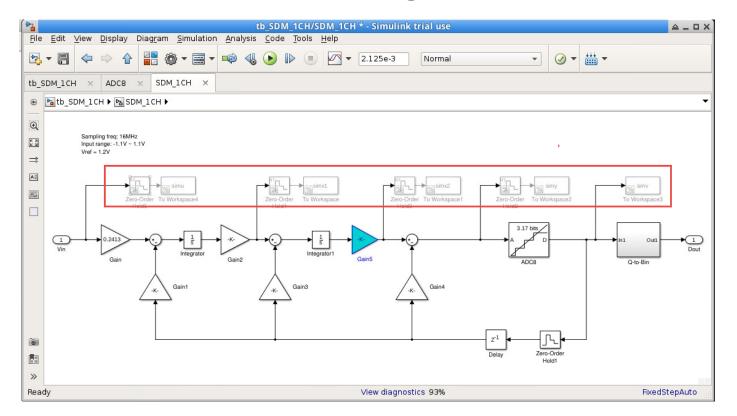

### **Digital Example: SDM DAC**

- □ Fixed Point Modeling is VERY powerful in Simulink

- □ Fixed point optimization and area/accuracy tradeoffs are rapidly analyzed

### **Digital DAC: Code Generation Video**

**Allegro Confidential Information**

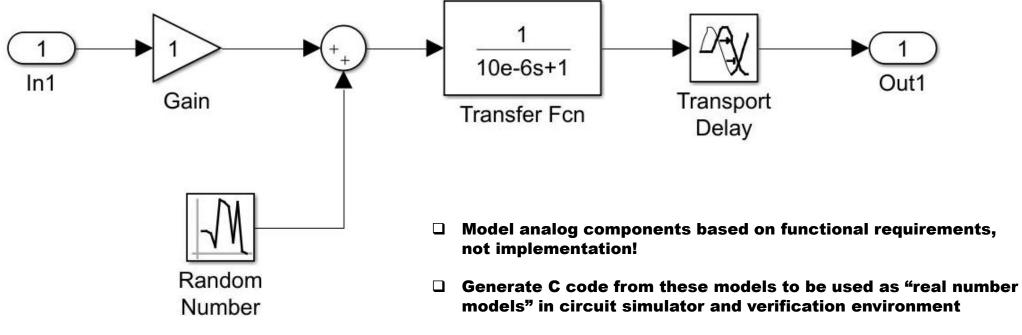

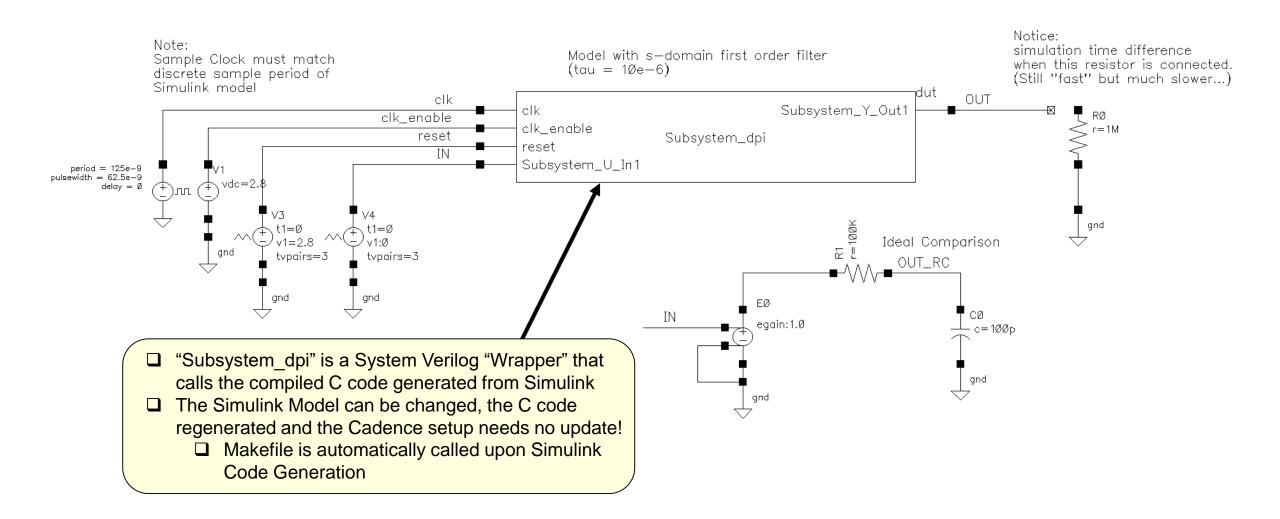

### Simulink Analog Models using DPI-C: Passive Filter with Noise and Delay

- □ This will allow for traceability and equivalence checking under the ISO26262 Automotive Specification.

- Analog designers will feel a strong attraction to SimElectronics.

Leave the implementation for the circuit simulator (Cadence, etc.)

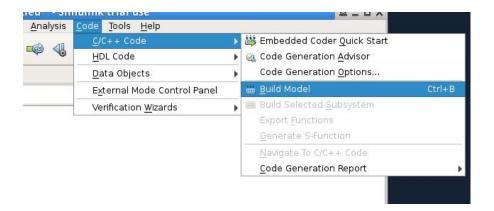

### Generate the System Verilog / C-code Model

| Solver       Data Import/Export         Optimization       Diagnostics         Hardware Implementation       Model Referencing         Simulation Target       Description:         System target file system/verilog DPI Component Generator       Description:         Build process       Browse         Report       Control of the system/verilog DPI Component Generator         Description:       System Varilog DPI Component Generator         Build process       Toolchain settings         Toolchain settings       Toolchain:         Automatically locate an installed toolchain       Validate         Debug       GNU gcc/g++ v4.4.x   gmake (64-bit Linux)         Build configuration:       Faster Runs         Code Alacement       Minimize run time         Data Type Replacement       Minimize run time         Data specification override       System strange classes         System defice dbjectives:       Unspecified         Ignore custom storage classes       Ignore test point signals         Code Generation Advisor       Prioritized objectives: Unspecified         Cekek model before generating code:       Off         Code only       Build | 🕲<br>🖪 Category 🛛 🖽 List                                                                                                                                                                                                                                                                                                           | Configura                                                                                                                                                    | ition Parameters: untitled/Cor                                                                                                                     | figuration (Active)      |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|

| Prioritized objectives: Unspecified       Set Objectives         Check model before generating code:       Off         Generate code only       Build                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Select:<br>Solver<br>Data Import/Export<br>) Optimization<br>Hardware Implementation<br>Model Referencing<br>) Simulation Target<br>Code Generation<br>Report<br>Comments<br>Symbols<br>Custom Code<br>Debug<br>Interface<br>Verification<br>Code Style<br>Templates<br>Code Placement<br>Data Type Replacement<br>Memory Sections | System target file s<br>Language:<br>Description: Sy<br>Build process<br>Toolchain settings<br>Toolchain:<br>Build configuration:<br>Data specification over | ystemVerilog DPI Component Gene<br>Automatically locate an installed<br>GNU gcc/g++ v4.4.x   gmake (64<br>Faster Runs<br>Minimize run time<br>ride | toolchain<br>-bit Linux) | <br>Validate |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                    | Prioritized objectives<br>Check model before                                                                                                                 | s: Unspecified<br>e generating code: Off                                                                                                           |                          | ck Model     |

### Select "systemverilog\_dpi\_ert.tlc"

#### □ Files to be generated □ Model\_name.sv "wrapper" □ Model\_name.so

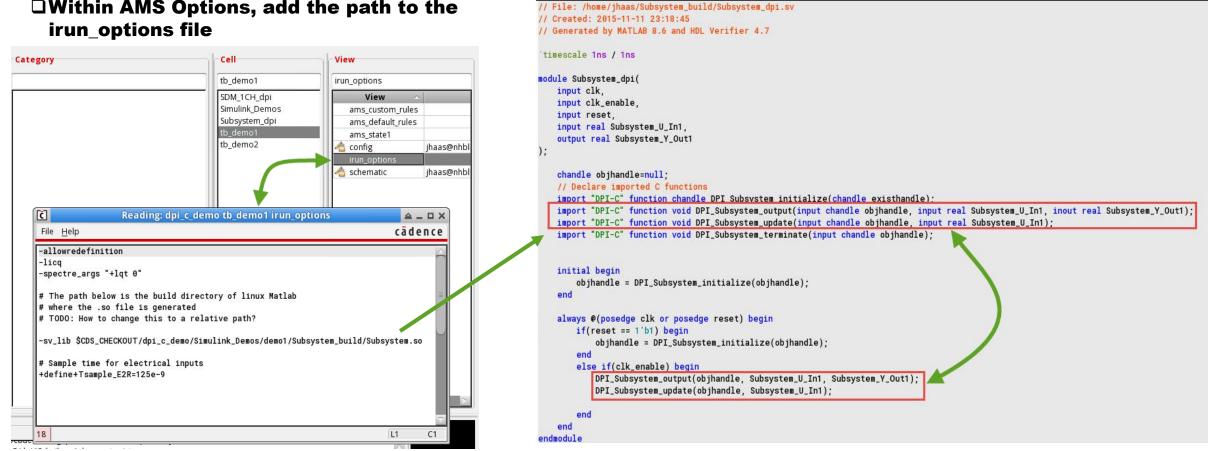

### The System Verilog Wrapper and the System Object Functions

## □ Within AMS Options, add the path to the

### **Cadence AMS Test Bench**

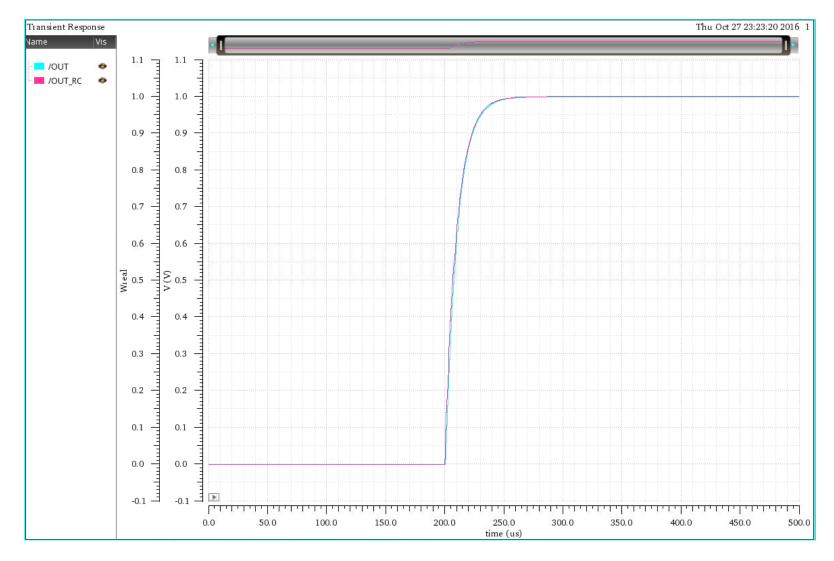

### Cadence Simulation of Simulink "C" Model and Ideal RC

Allegro Confidential Information

### Simulink Analog Models using DPI-C: Continuous Time Sigma Delta ADC

- Make sure and "comment out" any elements in the subsystem that you do not want in the generated code.

These elements are shown inside the red bay.

- □ Those elements are shown inside the red box.

## ASIC MBD Summary Present and Future

\*\*\*\*\*\*\*\*\*\*\*

- Simulink and Matlab have been instrumental in the development of an agile Automotive Mixed Signal ASIC Sensor Flow

- □ High level model exploration allows for accelerated insights and convergence on architecture and algorithms

- Traditional duplication efforts (model spec another model) are minimized

- Upfront models expedite the verification efforts and front load issue discovery

- Powerful Real Time Simulation Platforms (Speed Goat) allow for testing algorithms in the lab before design team is heavily engaged!

- Powerful modeling, automated code generation and robust traceability are paving the way for agile development in an ISO26262 world!

# **Thank You!**

## For more information: http://www.allegromicro.com

Email: jhaas@allegromicro.com