Hardware-Software Co-Design Overview

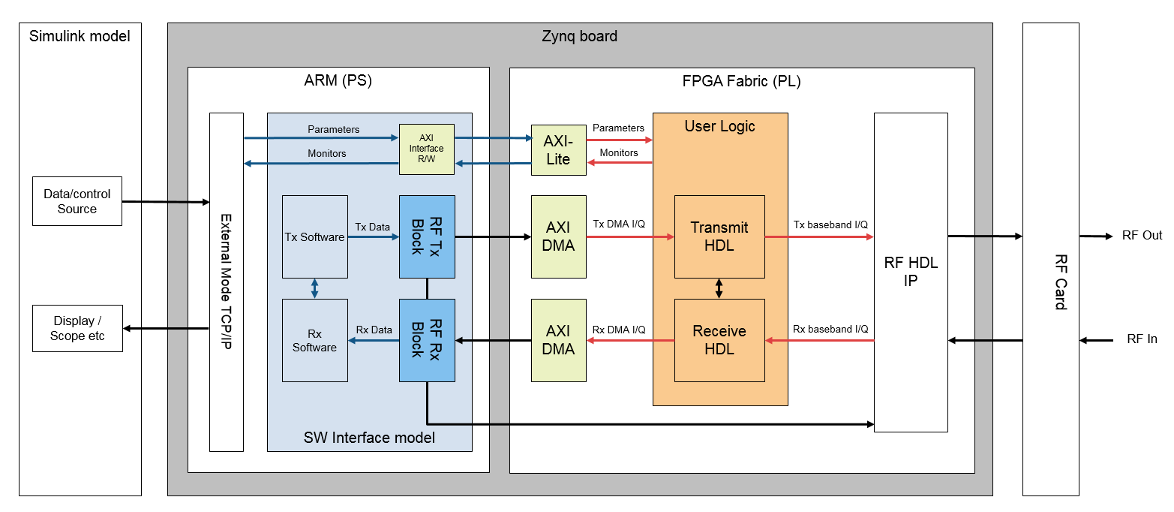

The hardware-software (HW/SW) co-design feature in this support package enables you to prototype an SDR algorithm on the USRP™ E3xx embedded series radio hardware. The implementation is partitioned between the ARM® processor and the FPGA fabric of the underlying Zynq® system on chip (SoC). In general, you use the ARM processor to implement slower-rate control functionality, and you use the FPGA fabric to implement high-rate signal processing. When the algorithm is deployed, you can control and tune parameters on the HDL logic.

In this diagram, the generated Transmit/Receive software blocks are placed in the

ARM section, ARM (PS), and the Transmit/Receive user logic

blocks are placed in the FPGA fabric section, Fabric (PL).

Software Requirements for HW/SW Co-Design

Note

The HW/SW co-design workflow is available in Simulink® only.

The HW/SW co-design workflow in the Communications Toolbox™ Support Package for USRP Embedded Series Radio requires additional software and third-party tools.

MathWorks Products

To target the FPGA fabric on the device: HDL Coder™ Support Package for AMD FPGA and SoC Devices (requires HDL Coder)

To target the ARM processor on the device: Embedded Coder® Support Package for AMD SoC Devices (requires Embedded Coder, Simulink Coder™, and Embedded Coder Support Package for ARM Cortex®-A Processors)

Third-Party Tools

Xilinx® Vivado® development tools, version 2024.1

Limitations

In single-channel mode, transmit and receive data frames must contain an even number of samples.

Default FPGA Resource Utilization on USRP E310

Get Started

To get started with the HW/SW co-design workflow in this support package:

Install the required additional software and third-party tools. See Installation for Hardware-Software Co-Design.

Follow the guided Hardware-Software Co-Design Workflow. To prototype SDR algorithms on the FPGA fabric only, follow the FPGA Targeting Workflow instead.

To learn more about the HW/SW co-design workflow on SoC platforms, see Hardware-Software Co-Design Workflow for SoC Platforms (HDL Coder).