Interval Test

Determine if signal is in specified interval

Libraries:

Simulink /

Logic and Bit Operations

Description

The Interval Test block outputs true (1) if the

input is between the values specified by the Lower limit and

Upper limit parameters. The block outputs false

(0) if the input is outside those values. The output of the block

when the input is equal to the Lower limit or the Upper

limit is determined by whether you select the Interval closed

on left and Interval closed on right check

boxes.

Examples

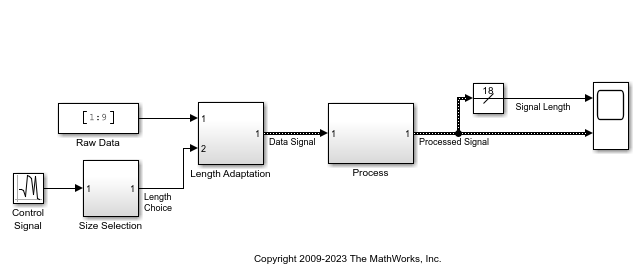

Variable-Size Signal Length Adaptation

Model showing how to change the length of a signal over time.

Ports

Input

Input signal, specified as a scalar, vector, matrix, or N-D array.

Limitations

When the input signal is an enumerated type, the Upper limit and Lower limit values must be of the same enumerated type.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated

Output

Output signal indicating whether the input values fall within the

specified interval. You can specify the Output data

type as boolean or

uint8.

Data Types: uint8 | Boolean

Parameters

When you select this check box, the Upper limit is

included in the interval for which the block outputs true

(1).

Programmatic Use

Block Parameter:

IntervalClosedRight |

| Type: character vector |

Values:

'on' | 'off' |

Default:

'on' |

The upper limit of the interval for which the block outputs true

(1).

Programmatic Use

Block Parameter:

uplimit |

| Type: character vector |

| Values: scalar | vector | matrix | N-D array |

Default:

'0.5' |

When you select this check box, the Lower limit is

included in the interval for which the block outputs true

(1).

Programmatic Use

Block Parameter:

IntervalClosedLeft |

| Type: character vector |

Values:

'on' | 'off' |

Default:

'on' |

The lower limit of the interval for which the block outputs true

(1).

Programmatic Use

Block Parameter:

lowlimit |

| Type: character vector |

| Values: scalar | vector | matrix | N-D array |

Default:

'-0.5' |

Specify the output data type as boolean or

uint8.

Programmatic Use

Block Parameter:

OutDataTypeStr |

| Type: character vector |

Values:

'boolean' | 'uint8' |

Default:

'boolean' |

Block Characteristics

Data Types |

|

Direct Feedthrough |

|

Multidimensional Signals |

|

Variable-Size Signals |

|

Zero-Crossing Detection |

|

Extended Capabilities

C/C++ Code Generation

Generate C and C++ code using Simulink® Coder™.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

| Architecture | Description |

|---|---|

Module (default) | Generate code for the subsystem and the blocks within the subsystem. |

BlackBox | Generate a black box interface. The generated HDL code includes only the input/output port definitions for the subsystem. Therefore, you can use a subsystem in your model to generate an interface to existing, manually written HDL code. The black-box interface generation for subsystems is similar to the Model block interface generation without the clock signals. |

| Remove the subsystem from the generated code. You can use the subsystem in simulation, however, treat it as a “no-op” in the HDL code. |

For the BlackBox architecture, you

can customize port names and set attributes of the external component

interface. See Customize Black Box or HDL Cosimulation Interface (HDL Coder).

| General | |

|---|---|

| AdaptivePipelining | Automatic pipeline insertion based on the synthesis tool, target frequency, and

multiplier word-lengths. The default is |

| ClockRatePipelining | Insert pipeline registers at a faster clock rate instead of the slower data rate. The

default is |

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| DistributedPipelining | Pipeline register distribution,

or register retiming. The default is |

| DSPStyle | Synthesis attributes for multiplier mapping. The default is |

| FlattenHierarchy | Remove subsystem hierarchy from generated HDL code. The default

is |

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SharingFactor | Number of functionally equivalent resources to map to a single shared resource. The default is 0. See also Resource Sharing (HDL Coder). |

| StreamingFactor | Number of parallel data paths, or vectors, that are time multiplexed to transform into serial, scalar data paths. The default is 0, which implements fully parallel data paths. See also Streaming (HDL Coder). |

If this block is not the DUT, the block property settings in the Target

Specification tab are ignored. In the HDL Workflow Advisor, if you use the

IP Core Generation workflow, these target specification block

property values are saved with the model. If you specify these target specification block

property values using hdlset_param, when you open HDL Workflow Advisor,

the fields are populated with the corresponding values.

| Target Specification | |

|---|---|

| AdditionalTargetInterfaces |

Additional target interfaces, specified as a character vector. To save this block property on the model, in the Set Target Interface task of the IP Core Generation workflow, corresponding to the DUT ports that you want to add more interfaces, select Add more.... You can then add more interfaces in the Add New Target Interfaces dialog box. Specify the type of interface, number of additional interfaces, and a unique name for each additional interface. Values: Example:

|

| ProcessorFPGASynchronization | Processor/FPGA synchronization mode, specified as a character vector. To save this block property on the model, specify the Processor/FPGA Synchronization in the Set Target Interface task of the IP Core Generation workflow. Values: Example: |

| TestPointMapping | To save this block property on the model, specify the mapping of test point ports to target platform interfaces in the Set Target Interface task of the IP Core Generation workflow. Values: Example: |

| TunableParameterMapping | To save this block property on the model, specify the mapping of tunable parameter ports to target platform interfaces in the Set Target Interface task of the IP Core Generation workflow. Values: Example: |

| AXI4RegisterReadback | To save this block property on the model, specify whether you want to enable readback on AXI4 subordinate write registers in the Generate RTL Code and IP Core task of the IP Core Generation workflow. To learn more, see Model Design for AXI4 Slave Interface Generation (HDL Coder). Values: |

| AXI4SlaveIDWidth |

To save this block property on the model, specify the number of AXI manager interfaces that you want to connect the DUT IP core to by using the AXI4 Slave ID Width setting in the Generate RTL Code and IP Core task of the IP Core Generation workflow. To learn more, see Define Multiple AXI Master Interfaces in Reference Designs to Access DUT AXI4 Slave Interface (HDL Coder). Values: |

| RegisterInterfaceReadPipeline |

To save this block property on the model, Specify the number of pipeline stages to insert in the read address decoder path by using the Register interface read pipeline setting in the Generate RTL Code and IP Core task of the IP Core Generation workflow. To learn more, see Model Design for AXI4 Slave Interface Generation (HDL Coder). Values: |

| GenerateDefaultAXI4Slave | To save this block property on the model, specify whether you want to disable generation of default AXI4 subordinate interfaces in the Generate RTL Code and IP Core task of the IP Core Generation workflow. Values: |

| IPCoreAdditionalFiles | Verilog®, SystemVerilog, or VHDL® files for black boxes in your design. Specify the full path to each file, and separate file names with a semicolon (;). You can set this property in the HDL Workflow Advisor, in the Additional source files field. Values: Example: |

| IPCoreName | IP core name, specified as a character vector. You can set this property in the HDL Workflow Advisor, in the IP core name field. If this property is set to the default value, the HDL Workflow Advisor constructs the IP core name based on the name of the DUT. Values: Example: |

| IPCoreVersion | IP core version number, specified as a character vector. You can set this property in the HDL Workflow Advisor, in the IP core version field. If this property is set to the default value, the HDL Workflow Advisor sets the IP core version. Values: Example: |

| IPDataCaptureBufferSize |

FPGA Data Capture buffer size, specified as a character vector. Use FPGA Data Capture to observe signals in a design when running on an FPGA. The buffer size uses values that are 128*2^n, where n is an integer. By default, the buffer size is 128 (n=0). The maximum value of n is 13, which means that the maximum value for buffer size is 1048576 (=128*2^13). Values: Example: |

PLC Code Generation

Generate Structured Text code using Simulink® PLC Coder™.

Fixed-Point Conversion

Design and simulate fixed-point systems using Fixed-Point Designer™.

Version History

Introduced before R2006a

See Also

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)