Multicore Modeling

The Infineon®AURIX™ TC4x microcontrollers contain six homogenous TriCore® CPUs (TriCore 0 to TriCore 5) and a heterogeneous Parallel Processing Unit (PPU). You can run different models on the available cores or you can partition complex models to run concurrently on these multiple cores to achieve design modularity. The Interprocess Data Channel block handles communication between the multiple cores. After simulating the multicore model, you can deploy the generated code on an Infineon AURIX TC4xx TriBoard using the SoC Builder tool and monitor the signals from the hardware using the One Eye tool from Infineon.

The PPU performs computations faster than the TriCores. The PPU core accelerates the performance of the model by using the code replacement libraries to replace parts of generated code with hardware-specific code. The TriCore 0 core is the principal core and it can communicate with all the remaining auxiliary cores (TriCore 1 to TriCore 5 and PPU).

See Getting Started with Multicore Modeling and Targeting for Infineon AURIX TC4x Microcontrollers example to understand how to validate, build, and run a multicore model.

Top-Level Models Using TriCores

You can create top-level models with referenced models using TriCore processing units to implement different application models. The Analyze Sensorless Observers for Field-Oriented Control Using Multiple Cores of Infineon AURIX example includes a top-level model with two referenced models using TriCore 0 and TriCore 1 processing units. The TriCore 0 referenced model implements a sensor-based field-oriented control (FOC) technique and the TriCore 1 referenced model implements different sensorless algorithms. The example uses the auxiliary core to analyze different sensorless observers without affecting the sensor-based model running on the TriCore 0.

If you select the Processing Unit of the top-model as

None, then the referenced models must have the same device build configuration to avoid conflict. The Package class, Pinout, Enable program cache, and Enable data cache parameters in such referenced models must match. For more information on setting up these configuration parameters, see Model Configuration Parameters.

Every participating core of the referenced models must have information on other participating cores of the application model. If you select the Processing Unit parameter of the top-model as

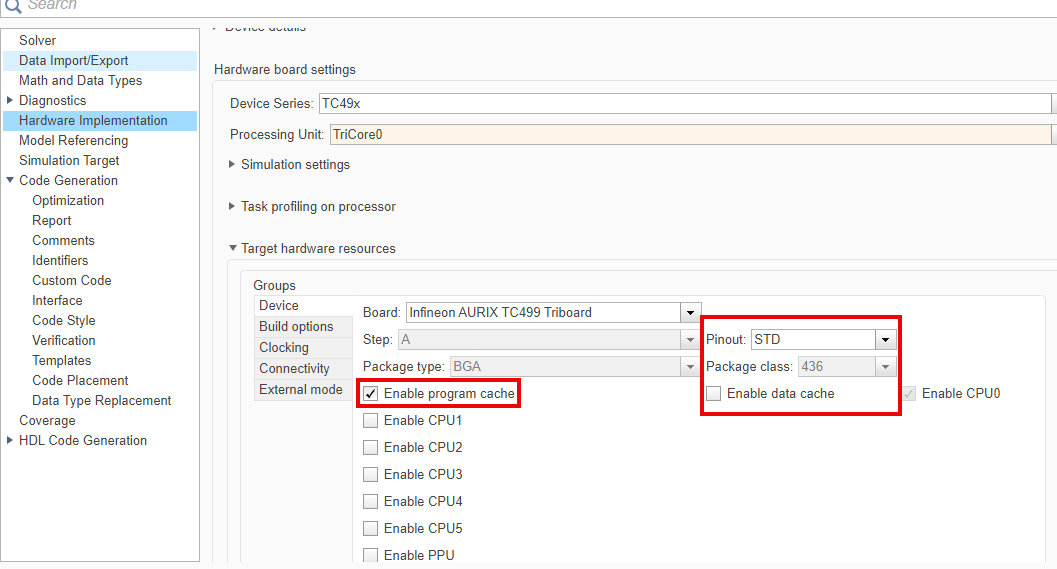

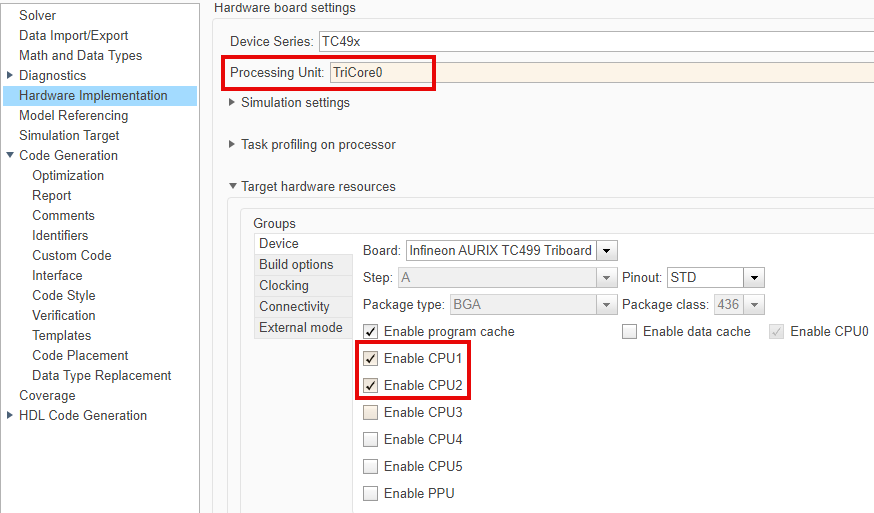

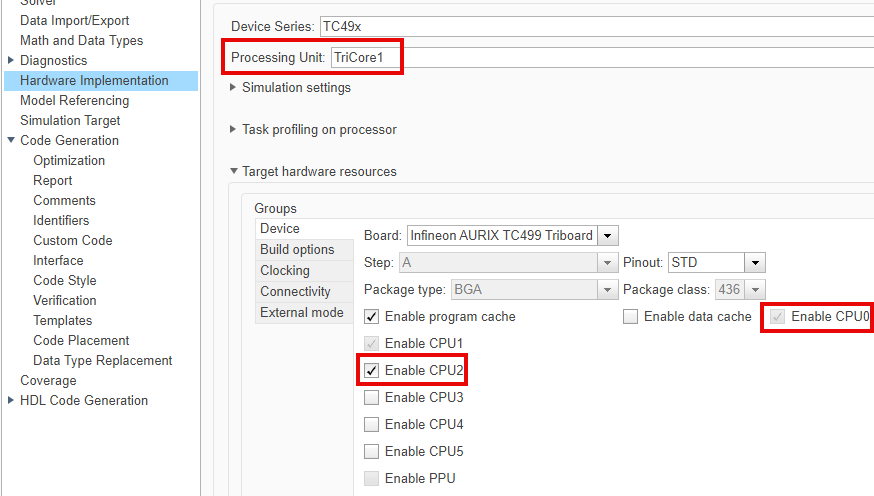

None, then Simulink® automatically configures the device settings for the top and referenced models. If you select the Processing Unit parameter of the top-model other thanNone, then you must manually set the device settings to ensure that every participating core has information about other participating cores.For example, consider a top-model with three referenced models using the TriCore 0, TriCore 1, and TriCore 2 processing units. To ensure that the TriCore 0 referenced model has information about other participating cores, select the Enable CPU 1 and Enable CPU 2 parameters in the Configuration Parameters window of the TriCore 0 referenced model.

Select the Enable CPU 2 and Enable CPU 1 parameters in the referenced models using the TriCore 1 and TriCore 2, respectively. By default, the Enable CPU 0 parameter is always selected in all the referenced models as the TriCore 0 core is the principal core.

Top-Level Models Using TriCores and PPU

You can create top-level models with referenced models using TriCores and a PPU to leverage the hardware-specific code generation functionality of the PPU.

The Getting Started with PPU Acceleration for Infineon AURIX TC4x Microcontrollers example includes a top-level model with two referenced models using the TriCore 0 and PPU cores. The PPU referenced model uses a function-call subsystem that uses a code replacement library (CRL) for the PPU to replace parts of the generated code with hardware-specific code. This CRL technique optimizes the PPU run time. You can partition the application model and use the PPU core to implement the partitioned model when you have large data processing and fast execution time requirements. For more information, see Code Replacement Library for PPU.

Single-Core and Flat Models Using TriCore and PPU

You can design single-core and flat models using the processing units of Infineon AURIX TC4x series microcontrollers. Since TriCore 0 is the principal core, single-core and flat models using auxiliary cores must always deploy the executable and linkable format (ELF) file of the TriCore 0 onto the Infineon AURIX TC4x hardware board.

Start-up Configuration Settings for Models Using Auxiliary Cores

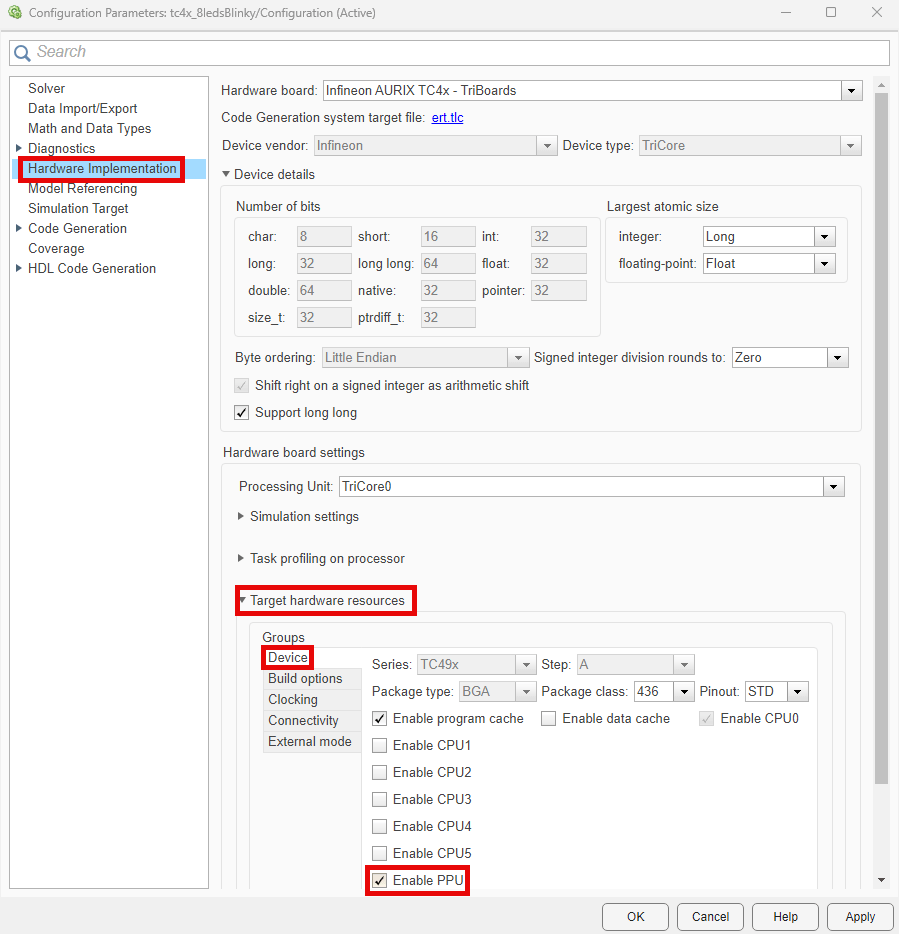

The auxiliary cores cannot start on their own and you must use a model based on Tricore 0 processing unit to activate the auxiliary cores. You can use the Getting Started with SoC Blockset Support Package for Infineon AURIX Microcontrollers example model to activate the required auxiliary core. In the Configuration Parameters window of the TriCore 0 model, enable the specific auxiliary core in the device settings and deploy the ELF file of TriCore 0 to the hardware board.

For example, the Code Verification and Validation with PIL Using PPU example uses the PPU core, which cannot start on its own. You can use the Getting Started with SoC Blockset Support Package for Infineon AURIX Microcontrollers example model, enable the PPU core in the device settings of the model, and deploy the ELF file of TriCore 0 to the hardware board before proceeding with PIL simulations.

See Also

Parallel Processing Unit | Hardware Mapping | SoC Builder | System on Chip (SoC)

Related Topics

- Getting Started with Multicore Modeling and Targeting for Infineon AURIX TC4x Microcontrollers

- Getting Started with PPU Acceleration for Infineon AURIX TC4x Microcontrollers

- Analyze Sensorless Observers for Field-Oriented Control Using Multiple Cores of Infineon AURIX

- Code Verification and Validation with PIL Using PPU