Developing Radio Applications for RFSoC with MATLAB and Simulink

In these videos, a MathWorks engineer uses a new Model-Based Design workflow to perform hardware-software partitioning using the example of a range-Doppler radar algorithm.

- Capabilities of Xilinx Zynq UltraScale+ RFSoC devices

- Challenges in hardware/software co-design

- System architecture simulation with SoC Blockset

- Overview of range-Doppler radar

- Developing reference models in Simulink

- Algorithm elaboration

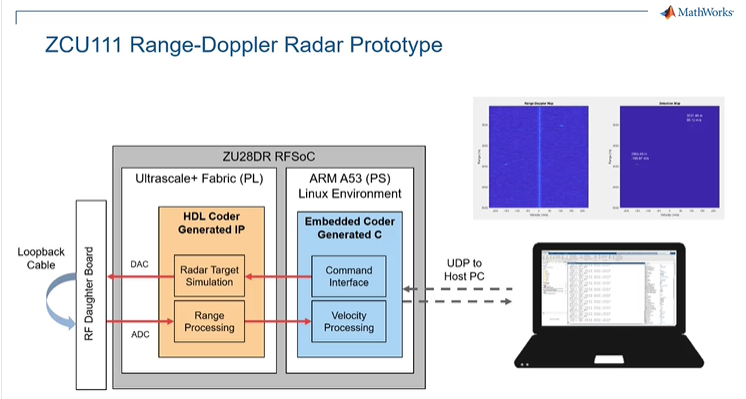

Target SoC architectures like Xilinx UltraScale+ RFSoC devices using Model-Based Design. Build Simulink models of hardware/software platforms to make design decisions.

System specifications for a range-Doppler radar are the driver for hardware/software implementation decisions when targeting SoC architectures like Xilinx RFSoC devices.

Perform simulation and analysis of the SoC architecture of the Xilinx RFSoC to investigate hardware/software partitioning of the range-Doppler radar algorithm.

Use SoC Blockset to automate the process of C and HDL code generation from Simulink models, and to automatically deploy the range-Doppler radar algorithm to a Xilinx ZCU111 development kit.