Diese Seite wurde maschinell übersetzt.

Füllen Sie bitte eine 1-Minuten-Befragung zur Qualität dieser Übersetzung aus.

Rambus entwickelt DSP-Blöcke für ASICs unter Verwendung von High-Level-Synthese mit HDL Coder

„Normalerweise können Verifizierungs- und Back-End-Teams erst mit der Integration beginnen, wenn die erste Version des spezifikationsbasierten RTL fertig ist, die möglicherweise noch Fehler enthält. Mit diesem auf HDL Coder basierenden Workflow kann HDL per Mausklick aus einem auf Systemebene verifizierten Modell generiert werden – das spart Monate und garantiert diesen Teams einen qualitativ hochwertigen Ausgangspunkt.“

Wichtigste Ergebnisse

- Der Designprozess wurde von einem Jahr auf drei Monate beschleunigt und die Produktivität durch die HDL-Codegenerierung gesteigert, wobei 80% des generierten Codes in der endgültigen Implementierung erhalten blieben.

- Die Entwicklung der Verifizierungsumgebung begann mit dem automatisch generierten RTL-Code und lief parallel zur benutzerdefinierten RTL-Entwicklung.

- Der Wechsel zwischen Designgenerationen oder Implementierungen derselben Generation erforderte nur begrenzte Änderungen am HDL-fähigen Simulink-Modell.

Heutige Kommunikationsgeräte enthalten komplexe Signalverarbeitungsalgorithmen, die in anwendungsspezifischen integrierten Schaltkreisen (ASICs) implementiert sind, um eine höhere Leistung, geringere Endproduktkosten und einen geringeren Stromverbrauch zu erzielen. Der physische Implementierungsprozess für ASICs ist langwierig. Er beginnt, bevor die RTL-Verifizierung abgeschlossen ist, und erfordert die manuelle Integration optimierter Addierer und Multiplizierer sowie RTL-Debug- und Beobachtungsfunktionen.

Ehud Nir, Direktor für Digital Engineering bei Rambus, musste mit begrenzter Zeit und begrenzten technischen Ressourcen den DSP für einen Gen6 PCIe PHY entwickeln. Bei einem früheren Projekt für ein vergleichbares Design waren ein ASIC-Designer, der RTL-Code schrieb, und ein Verifizierungsingenieur, der Testumgebungen entwickelte, zwölf Monate lang an der Arbeit beteiligt. Da der Systemarchitekt MATLAB® und Simulink® verwendet hatte, um den vollständigen Gen6-Serialisierer/Deserialisierer (SerDes) einschließlich des DSP zu modellieren, beschloss Ehud, den Designprozess zu beschleunigen, indem er mit HDL Coder™ direkt aus dem Simulink-Modell eine RTL-Referenz für die ASIC-Implementierung generierte.

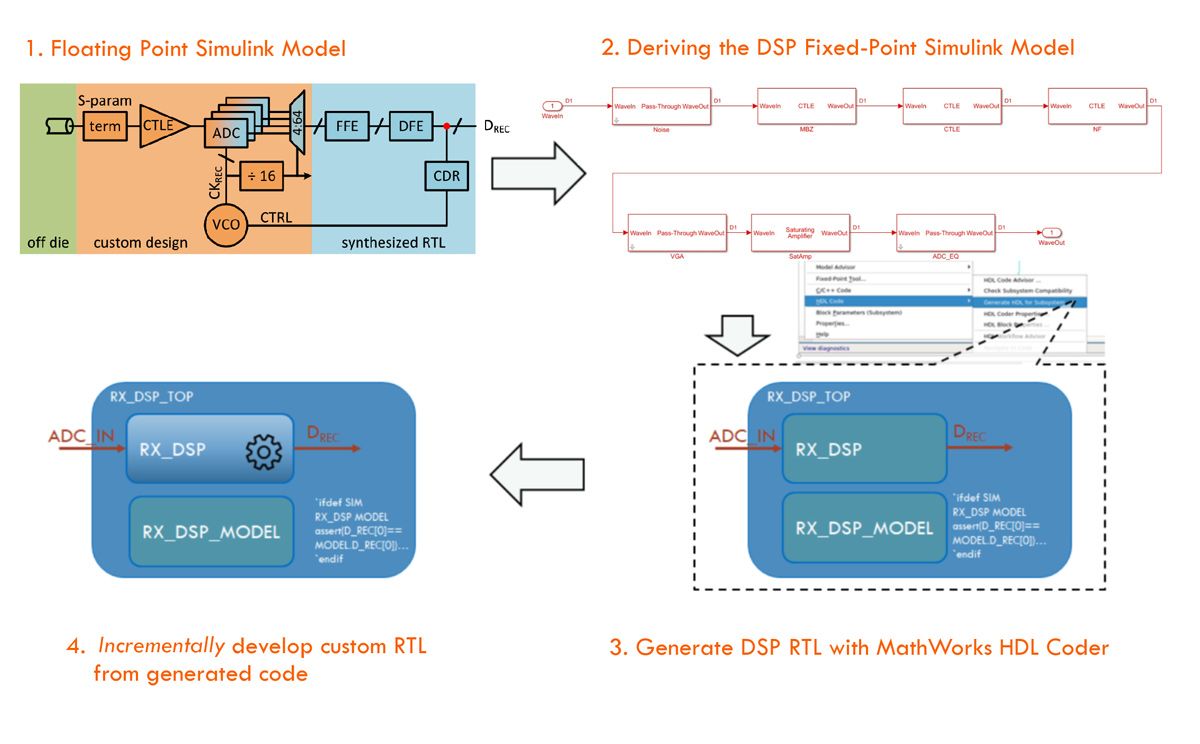

Zu Beginn konvertierte der Systemarchitekt das Gleitkomma-Simulink -Modell des SerDes DSP in ein Festkomma-Modell. Nachdem sichergestellt wurde, dass dieses Modell die elektrischen Zielspezifikationen und -eigenschaften erfüllte, generierte ein digitaler ASIC-Designer mithilfe von HDL Coder RTL-Code aus dem Festkommamodell. Dieses Referenzmodell wurde während des Designprozesses aufgrund veränderter Anforderungen, wie beispielsweise Änderungen am digitalen Front-End-Filter, mehrmals aus Simulink neu generiert.

Der von HDL Coder generierte RTL-Code diente dem Verifizierungsteam als Referenzpunkt für die Verifizierung auf IP-Ebene und den Back-End-Teams für den Beginn des physischen Designs. In der Zwischenzeit hat der Digitaldesigner den RTL-Code angepasst, indem er die kombinatorische und sequentielle Logik entwickelt hat, um den Stromverbrauch zu senken und Energiesparmodi hinzuzufügen. Durch die Verwendung des generierten RTL als Referenz wurde ein vollständiger hierarchischer Vergleich zwischen dem benutzerdefinierten RTL und der generierten RTL-Referenz ermöglicht. Mit zusätzlichen Assertionen konnte das benutzerdefinierte RTL mithilfe von HDL-Simulatoren überprüft werden, um sicherzustellen, dass es dem Referenzmodell bitzyklusgenau entsprach. Dadurch konnte ein einzelner Ingenieur in weniger als drei Monaten eine vollständig verifizierte, zeitsaubere DSP-Netzliste erstellen, während am früheren Projekt zwei Ingenieure 12 Monate lang arbeiteten. Der von diesem DSP betriebene Gen6 PHY ASIC-Testchip wurde im Labor erfolgreich auf Anhieb validiert.

Eingesetzte Produkte