Generate Code and Synthesize on FPGA Using HDL Workflow Advisor

The HDL Workflow Advisor guides you through the stages of generating HDL code for a Simulink® subsystem and the FPGA design process, such as:

Checking the model for HDL code generation compatibility and automatically fixing incompatible settings.

Generation of HDL code, a test bench, and scripts to build and run the code and test bench.

Generation of cosimulation or SystemVerilog DPI test benches and code coverage (requires HDL Verifier™).

Synthesis and timing analysis through integration with third-party synthesis tools.

Back-annotation of the model with critical path information and other information obtained during synthesis.

Complete automated workflows for selected FPGA development target devices, including FPGA-in-the-loop simulation (requires HDL Verifier), and the Simulink Real-Time™ FPGA I/O workflow.

FIR Filter Model

This example illustrates how you can generate HDL code for the FIR filter model and synthesize the design on an FPGA device. Before you generate HDL code, the model must be compatible for HDL code generation. To check and update your model for HDL compatibility, see Check HDL Compatibility of Simulink Model Using HDL Code Advisor. HDL Workflow Advisor is not available in Simulink Online™.

This example uses the Symmetric FIR filter model that is compatible for HDL code generation. To open this model at the command line, enter:

sfir_fixed

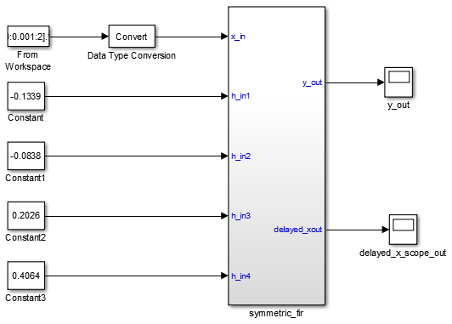

The model uses a division of labor that is suitable for HDL design.

The

symmetric_firsubsystem, which implements the filter algorithm, is the device under test (DUT). An HDL entity is generated from this subsystem.The top-level model components that drive the subsystem work as a test bench.

The top-level model generates 16-bit fixed-point input signals for the

symmetric_fir subsystem. The Signal From Workspace block generates a

test input (stimulus) signal for the filter. The four Constant blocks provide

filter coefficients. The Scope blocks are used for simulation and are not

used for HDL code generation.

To navigate to the symmetric_fir subsystem,

enter:

open_system('sfir_fixed/symmetric_fir')

Create a Folder and Copy Relevant Files

In MATLAB®:

Create a folder named

sl_hdlcoder_work, for example:mkdir C:\work\sl_hdlcoder_worksl_hdlcoder_workstores a local copy of the example model and folders and generated HDL code. Use a folder location that is not within the MATLAB folder tree.Make the

sl_hdlcoder_workfolder your working folder, for example:cd C:\work\sl_hdlcoder_workSave a local copy of the

sfir_fixedmodel to your current working folder. Leave the model open.

Set Up Tool Path

If you do not want to synthesize your design, but want to generate HDL code, you do not

have to set the tool path. In the HDL Workflow Advisor, on the Set Target > Set Target Device and Synthesis Tool step, leave the Synthesis tool setting to the default

No Synthesis Tool Specified, and then run the workflow.

If you want to synthesize your design on a target platform, before you open the HDL

Workflow Advisor and run the workflow, set up the path to your synthesis tool. This example

uses Xilinx®

Vivado®, so you must have already installed Xilinx

Vivado. To set the tool path, use the hdlsetuptoolpath function to point to an installed Xilinx

Vivado executable. Optionally, you can use a different synthesis tool of your choice

and follow this example. To set the path to that synthesis tool, use

hdlsetuptoolpath. To learn about the latest supported tools, see

HDL Language Support and Supported Third-Party Tools and Hardware.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2024.1\bin\vivado.bat');

Open the HDL Workflow Advisor

To start the HDL Workflow Advisor from a Simulink model,

In the Apps tab, select HDL Coder. The HDL Code tab appears.

Select the DUT Subsystem in your model, and make sure that this Subsystem name appears in the Code for option. To remember the selection, you can pin this option. Click Workflow Advisor.

When you open the HDL Workflow Advisor, the code generator might warn that the project folder is incompatible. To open the Advisor, select Remove slprj and continue.

In the HDL Workflow Advisor, the left pane lists the folders in the hierarchy. Each folder represents a group or category of related tasks. From the left pane, you can select a folder or an individual task. The HDL Workflow Advisor displays information about the selected folder or task in the right pane.

To learn more about each individual task, right-click that task, and select What's This?.

To learn more about the HDL Workflow Advisor window, see Getting Started with the HDL Workflow Advisor.

Generate HDL Code and Synthesize on FPGA

In the Set Target > Set Target Device and Synthesis Tool step, for Synthesis tool, select

Xilinx Vivadoand select Run This Task.To generate code, right-click the Generate RTL Code and Testbench task, and select Run to Selected Task.

In the FPGA Synthesis and Analysis > Perform Synthesis and P/R > Run Implementation task, clear Skip this task and click Apply.

Right-click the Annotate Model with Synthesis Result and select Run to Selected Task.

Run Workflow at Command Line with a Script

To run the HDL workflow at a command line, you can export the Workflow Advisor settings to a script. To export to script, in the HDL Workflow Advisor window, select File > Export to Script. In the Export Workflow Configuration dialog box, enter a file name and save the script.

The script is a MATLAB file that you can run from the command line. You can modify the script directly or, import the script into the HDL Workflow Advisor, modify the tasks, and export the updated script. To learn more, see Run HDL Workflow with a Script.