Performance Report

Display performance and core usage metrics after model simulation or execution on SoC device

Since R2021b

Description

The Performance Report app displays summaries of task executions, core usage of the processor, and memory performance diagnostics. You can use the report after model simulation or after execution on a hardware processor.

This app displays the following information:

Task Activity

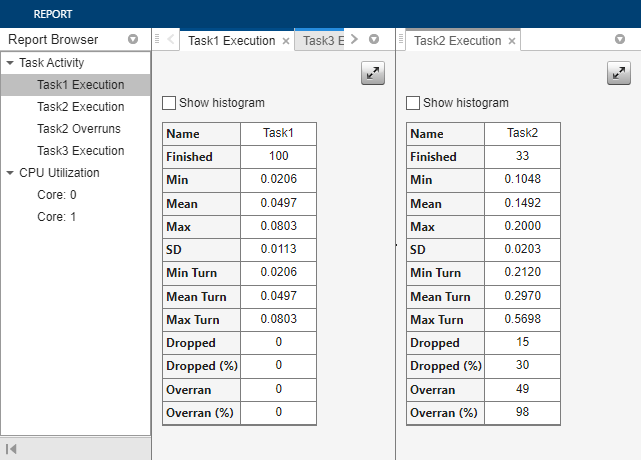

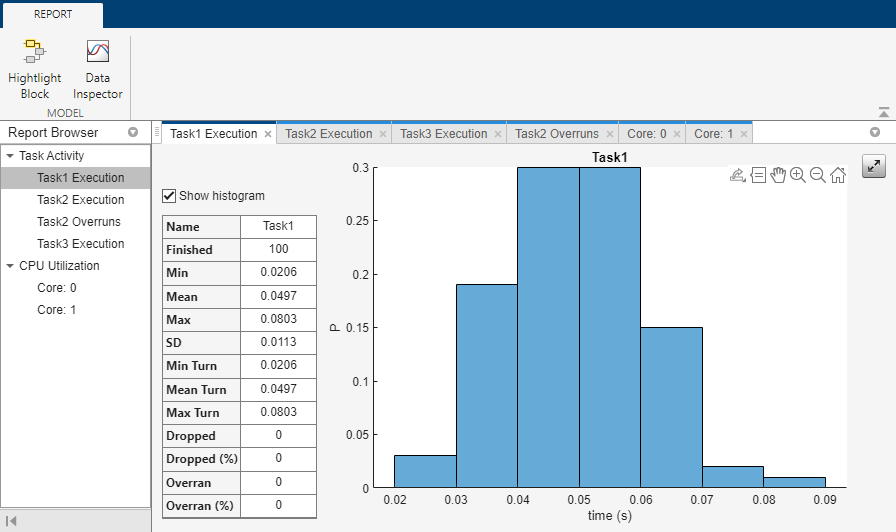

When the design includes a Task Manager block, you can view the following information for each task:

Total executions per task

Minimum, mean, maximum, and standard deviation (SD) of execution times per task

Minimum, mean, and maximum turnaround times per task

Total and percentage of dropped task instances

Total and percentage of overrun task instances

Task distribution per processor core

You can also select a view of task overruns, which has these features:

Time instance when the task should have run

Indication if the task overrun resulted in a task drop

Filter switch to Show only dropped tasks for a more focused analysis

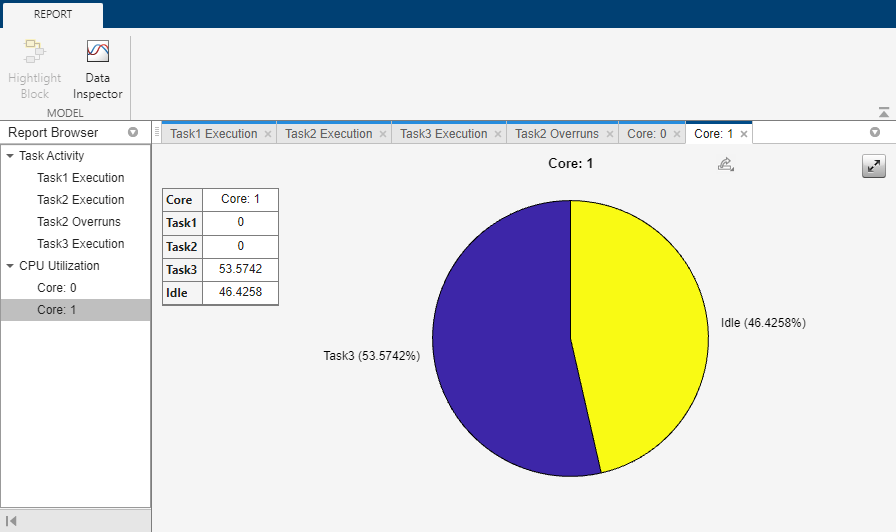

CPU Utilization Per Core

Active time for each task

Core idle time

Memory Utilization

If memory logging is enabled, and the design includes a Memory Controller block with one of these memory channel blocks:

You can view the following information for each memory channel:

Bandwidth, burst, and latency information per Memory Controller block.

Completion of buffer read or write

Completion of task execution

To enable memory logging:

In the Simulink® toolstrip, expand the Prepare section and select Profile Memory.

Make sure that the memory block that you are using is set to burst-accurate simulation.

When executing on an SoC, you must also enable logging with an AXI monitor. To enable that, select Hardware Settings in the toolstrip. Then, navigate to Hardware Implementation > Target hardware resources > FPGA design (debug) and select Include AXI interconnect monitor.

Interprocess Data Channel Statistics

When an Interprocess Data Channel, Interprocess Data Read, or Interprocess Data Write block is in the design, you can view the following information for each interprocess data channel:

Block name

Number of buffers

Maximum number of buffers used

Total overwritten buffers

The memory utilization plots are calculated measurements from a simulation of your model. The plots consider the data type, sample time, and clock frequency to calculate the bandwidth of your memory model and considers the number of bursts executed per memory port.

Open the Performance Report

Simulink Toolstrip: On the System on Chip tab, click Performance Report.