cosimulationConfiguration

Description

The cosimulationConfiguration object controls the creation of an

HDL Cosimulation block or System object™ for a specified HDL module.

Creation

Syntax

Description

cosimObj = cosimulationConfiguration(HDLSimulator,SubWorkflow,HDLTopLevelName)cosimulationConfiguration object with the specified

HDLSimulator, SubWorkflow, and

HDLTopLevelName values.

This workflow is a command-line alternative to using the Cosimulation Wizard for creating an HDL

Cosimulation block or an hdlverifier.HDLCosimulation

System object.

cosimObj = cosimulationConfiguration(MATfile)cosimulationConfiguration object based on the results of a

previous run of the Cosimulation Wizard or command-line

workflows.

Properties

Workflow

HDL simulator to use for cosimulation, specified as

'ModelSim', 'Xcelium', 'Vivado

Simulator', or 'VCS'.

Kind of cosimulation to perform:

'Simulink'— Configures the workflow to create an HDL Cosimulation block for a Simulink® cosimulation.'MATLAB System Object'— Configures the workflow to create anhdlverifier.HDLCosimulationSystem object for a MATLAB® cosimulation.

Name of the top level HDL module or entity, specified as a string or character vector.

Data Types: char | string

HDL Compilation

HDL directory, file, or files required for cosimulation, specified as a string or cell array. If one of the files does not have a known HDL file extension, the tool ignores it.

Example: './hdlsrc' includes all files from the

hdlsrc directory

Example: {'./hdlsrc','myModule.v'} includes all files from the

hdlsrc directory and a local file named

myModule.v.

Another option, is to specify a list where each file is followed by a file type. Available file types depend on the simulator:

ModelSim™:

Verilog(*.v, *.sv),VHDL(*.vhd),ModelSim macro file(*.do)Xcelium™:

Verilog(*.v, *.sv),VHDL(*.vhd),Shell script(*.sh)Vivado®:

Verilog(*.v, *.sv),VHDL(*.vhd),Vivado XCI file(*.xci)VCS®:

Verilog(*.v, *.sv),VHDL(*.vhd),PLI tab file(*.tab)

Example: {'mytop.v','Verilog','submod.v','Verilog'}

Data Types: char | string | cell array

Location of the HDL simulator, specified as a string or character vector. Use this

option when you want to use a simulator in a different location than the one specified

on the system PATH. When the argument is empty, the system path is

used.

Data Types: char | string

Specify flags for VCS

vhdlan tool.

Dependencies

To enable this property, set HDLSimulator to

'VCS'.

Data Types: char | string

Specify flags for VCS

vlogan tool.

Dependencies

To enable this property, set HDLSimulator to

'VCS'.

Data Types: char | string

Compilation commands to use, specified as a string or character vector. The compilation commands are automatically generated based on the selected simulator and design file list. You can supply different compilation commands if required, for example, when you have to compile into a specific library.

Tip

It is useful to run the workflow once to generate a

cosimWizard_<TOP>.mat file. Then you can modify the

compilation commands and set this property.

Dependencies

When HDLSimulator is set to 'VCS', this

property is disabled.

Data Types: char | string

Include a parameter file to specify nondefault values for HDL parameters or

generics. Edit the file to override values from their defaults and execute the

runWorkflow function for the parameter values to be in effect.

You can enter one of these options:

''— Generates a default parameter file namedparameter_, whereHDLTopLevelName.cfgHDLTopLevelNameis the name of the top-level HDL module or entity. The file includes a line for each HDL parameter and all the lines are commented. When you execute therunWorkflowfunction, the function generates the default file and continues running through the whole workflow.'GENERATE_AND_EDIT'— Generates a new parameter file with the default filenameparameter_. When executing theHDLTopLevelName.cfgrunWorkflowfunction, the execution stops after generating the parameter configuration file. Edit the file to uncomment the lines with relevant parameters and change their value to override the default value. Then, restart the workflow by executingrunworkflow(c)in the command line.filename — Uses the specified parameter file when you execute the workflow.

This property is valid only for cosimulation with VCS, Xcelium or ModelSim simulators.

Tip

To set HDL parameters when using the Vivado simulator, use the HDLCompilationCommand property. For more information see Set HDL Parameters for Vivado Simulation.

Data Types: char | string

Options for the HDL elaboration tool, specified as a string or character vector.

Dependencies

This property is valid for cosimulation with VCS or Xcelium.

Data Types: char | string

Options for the HDL simulation tool, specified as a string or character vector.

The default value for Xcelium forces use of the 64-bit app.

The default value for ModelSim includes the necessary flags to define the HDL time precision and to give read/write access of the port for cosimulation.

Dependencies

This property is valid for cosimulation with Xcelium, VCS, or ModelSim.

Data Types: char | string

HDL Timing

Time unit for HDL simulation. This unit affects the following configurations:

PreCosimulationRunTimepropertySampleTimeproperty (MATLAB System object sub-workflow)Period attribute of clock ports

Duration attribute of reset ports

The default unit is determined dynamically by a query of the time precision to

the HDL simulator during compilation (ModelSim, Xcelium) or by the HDLTimePrecision property (Vivado).

Note

The SampleTime attribute of output ports is in seconds

because it specifies a Simulink time.

The amount of time to run the HDL simulator before beginning simulation in Simulink or MATLAB, in HDLTimeUnit units. This time allows getting through any necessary resets and asserting clock enables.

A visual timing diagram of clocks, resets, and the cosimulation start time is

created in file hdlverifier_rstclk_waveform.jpg after you run the

workflow.

Automatically determine the ratio between Simulink time to HDL time at the first cosimulation.

The Simulink sample times are related to the HDL simulation time using a timing scale. Often the best choice is for the fundamental Simulink sample time to equal the fastest clock period in the HDL. Because all of the input sample times are not known at the time that this workflow executes, you can choose to have the timescale determined automatically on the first simulation when all of the sample times are known.

Dependencies

To enable this property, set Subworkflow to

'Simulink'.

This property is not available for cosimulation with VCS.

Manually set the timescale, specified as a scale factor and a time unit:

{factor, unit}.

The scale is relative to 1 second in Simulink: 1 second in Simulink is equal to {factor, unit} in HDL. The factor is a

double and the unit is one of 'fs','ps','ns','us','ms', or

's'. The default value is {1, 's'}, which

means that Simulink times are equivalent to HDL times.

Example: With a Simulink sample time of 1 second and an HDL clock of 100 MHz, create a timescale

where 1 second in Simulink is equal to 10 ns in HDL: c.AutoTimeScale = false; c.TimeScale

= {10, 'ns'};

Dependencies

To enable this property, set Subworkflow to

'Simulink'.

Set the MATLAB sample time for the generated System object in HDLTimeUnit

units. All inputs and outputs share the same sample time in MATLAB and each call to the step method elapses this

amount of time.

The default value is determined by the specified clock periods and output sample times.

Dependencies

To enable this property, set Subworkflow to 'MATLAB

System Object'.

HDL Simulator Connection

Channel type for connecting to MATLAB or Simulink to the HDL simulator, specified as Socket or

Shared Memory.

Socket: MATLAB or Simulink and the HDL simulator communicate through a designated TCP/IP socket. You can use it for single-system and network configurations. This option offers the greatest scalability. For more information about TCP/IP socket communication, see TCP/IP Socket Ports.Shared memory: MATLAB or Simulink and the HDL simulator communicate through shared memory. Shared memory communication provides optimal performance.When

HDLSimulatoris set to'VCS', this option is not available.

Port Interface Properties

Expression for auto-assigning ports to clocks, specified as a regular expression. For more information about regular expressions in MATLAB, see Regular Expressions.

Example: 'clk_in$' assigns all the ports that end with "clk_in"

as clock ports.

Expression for auto-assigning ports to resets, specified as a regular expression. For more information about regular expressions in MATLAB, see Regular Expressions.

Example: c.ResetPortRegularExpression = [c.ResetPortRegularExpress

'rst[0-9]$'] assigns all the ports that end with "rst" and a numerical

value as reset ports, in addition to the default expression for reset

ports.

Expression for labeling ports as unused, specified as a regular expression. Ports assigned as unused are not part of the cosimulation. Unused ports do not show up in the cosimulation interface and are not driven or sampled.

To clear the specifications, provide an empty argument after the signal names.

For more information about regular expressions in MATLAB, see Regular Expressions.

Example: 'clk_out$' indicates that any ports that end with

"clk_out" are unused.

This property is read-only.

Input ports, displayed as a table. See the full table contents by calling the

portInterface object function.

The default is an empty table and the workflow determines input data ports. Inputs that do not match the clock, reset, and unused regular expressions are considered input data ports.

You can explicitly assign input ports by using the specifyInput object function.

This property is read-only.

Output ports, displayed as a table. Each row in the table contains the following information per output:

Name of output port

SampleTimeDataTypeSignedFractionLength

In addition to the DUT outputs, the table includes a row named

default_output_definition, which contains the default values

assigned for the outputs.

You can change the default output values or manually assign output ports by using

the specifyOutput object function.

See the full table contents by calling the portInterface object function.

This property is read-only.

Clock ports, displayed as a table. Each row in the table contains the following information per clock:

Name of clock port

EdgePeriod

In addition to the DUT clocks, the table includes an extra row named

default_clock_definition for the default clock

definitions.

You can change the default clock values or manually assign clocks by using the

specifyClock object function.

See the full table contents by calling the portInterface object function.

This property is read-only.

Reset ports, displayed as a table. Each row in the table contains the following information per reset:

Name— Name of reset portInitialValue— Initial value of the resetDuration— Duration of the reset signal

In addition to the DUT resets, the table includes an extra row named

default_reset_definition for the default reset

definitions.

You can change the default reset values or manually assign resets by using the

specifyReset object function.

See the full table contents by calling the portInterface object function.

This property is read-only.

Unused ports, displayed as a table. See the full table contents by calling the

portInterface object function.

The default is an empty table and the workflow determines the unused ports. Ports that match the unused regular expression are considered unused.

You can explicitly label ports as unused by using the specifyUnused object function.

Object Functions

portInterface | Display port specifications |

runWorkflow | Execute cosimulation workflow and generate required artifacts |

specifyClock | Assign clock ports to cosimulation block or System object |

specifyInput | Assign HDL input ports to cosimulation block or System object |

specifyOutput | Assign HDL output ports to cosimulation block or System object |

specifyReset | Assign reset ports to cosimulation block or System object |

specifyUnused | Label HDL ports as unused ports |

Examples

This example shows how to cosimulate a raised cosine filter in Simulink® using the command-line interface. It follows the same workflow to generate cosimulation artifacts as in Get Started with Simulink HDL Cosimulation, but it uses the command line instead of the Cosimulation Wizard.

Configure Cosimulation Workflow

Create a cosimulation configuration object.

c = cosimulationConfiguration('ModelSim','Simulink','rcosflt_rtl');

Set up the HDL file.

c.HDLFiles = {'./rcosflt_rtl.v','Verilog'};

Set the filter_out port as an output with a signed fixed-point data-type, and set the fraction length to 29.

specifyOutput(c,'filter_out',Datatype='Fixedpoint',Signed=true,FractionLength=29)

Set the clock to a period of 20 ns, and set the reset duration to 15 ns.

specifyClock(c,'clk',Period=20) specifyReset(c,'reset',Duration=15)

Display the port table. It reflects the settings just made for output, clock, and reset attributes. The other design ports will take on default attributes.

portInterface(c);

----- Input Data Ports -----

0×1 empty table

Name

____

----- Output Data Ports -----

2×5 table

Name SampleTime DataType Signed FractionLength

_____________________________ __________ ______________ ______ ______________

{'default_output_definition'} 1 {'Inherit' } false 0

{'filter_out' } 1 {'Fixedpoint'} true 29

----- Clock Ports -----

2×3 table

Name Edge Period

____________________________ __________ ______

{'default_clock_definition'} {'Rising'} 10

{'clk' } {'Rising'} 20

----- Reset Ports -----

2×3 table

Name InitialValue Duration

____________________________ ____________ ________

{'default_reset_definition'} 1 8

{'reset' } 1 15

----- Unused Ports -----

0×1 empty table

Name

____

Generate HDL Cosimulation Block

Run the workflow to generate an HDL Cosimulation block and the accompanying files.

runWorkflow(c);

-------------------- Step 1------------------

Select the type of cosimulation you want to do.If the HDL simulator executable you want to use is not on the system path in your environment you must specify its location.

-------------------- Step 2------------------

Add all VHDL, Verilog, and/or script files to be used in cosimulation to the following table. If the file type cannot be automatically detected or the detection result is incorrect, specify the correct file type in the table. If possible, we will determine the compilation order automatically using HDL simulator provided functionality. Then the HDL files can be added in any order.

-------------------- Step 3------------------

HDL Verifier has automatically generated the following HDL compilation commands. You can customize these commands with optional parameters as specified in the HDL simulator documentation but they are sufficient as shown to compile your HDL code for cosimulation. The HDL files will be compiled when you click Next.

Compiling HDL design. Please wait ...

###Compiling HDL design

Reading pref.tcl

# 2024.2

# do hdlverifier_compile_design.do

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# Loading project compile_project

# .

# QuestaSim-64 vlog 2024.2 Compiler 2024.05 May 20 2024

# Start time: 14:09:05 on Aug 29,2025

# vlog -work work -vopt C:/Users/user/OneDrive - MathWorks/Documents/MATLAB/ExampleManager/user.Bdoc25b.j2987061/hdlverifier-ex80882452/rcosflt_rtl.v

# -- Compiling module rcosflt_rtl

#

# Top level modules:

# rcosflt_rtl

# End time: 14:09:07 on Aug 29,2025, Elapsed time: 0:00:02

# Errors: 0, Warnings: 0

# Compile of rcosflt_rtl.v was successful.

# All compile dependencies have been resolved.vlog -work work -vopt -stats=none {C:/Users/user/OneDrive - MathWorks/Documents/MATLAB/ExampleManager/user.Bdoc25b.j2987061/hdlverifier-ex80882452/rcosflt_rtl.v}

# reading E:/share/apps/HDLTools/ModelSim/questasim-2024.2/Windows/win64/../modelsim.ini

# QuestaSim-64 vlog 2024.2 Compiler 2024.05 May 20 2024

# -- Compiling module rcosflt_rtl

#

# Top level modules:

# rcosflt_rtl

...done

-------------------- Step 4------------------

Use 'Shared Memory' communication method if your firewall policy does not allow TCP/IP socket communication.

Elaborating and Loading HDL simulation image. Please wait ...

Waiting for HDL Simulator to startup ...

120 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

119 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

118 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

117 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

116 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

115 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

114 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

113 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

Waiting for HDL Simulator to startup ...

112 seconds to time-out ...

To stop this process, press Ctrl+C in MATLAB console.

...done

-------------------- Step 5------------------

Specify all input and output port types. Input signals that are identified as 'Clock' and 'Reset' signals will be forced in the HDL simulator through Tcl commands. You can specify the timing parameters for forced 'Clock' and 'Reset' signals in the next step. If you want to drive your HDL clock and reset signals with Simulink signals, mark them as 'Input'.

-------------------- Step 6------------------

Set the sample time and data type for each output port. You can specify the sample time as -1, which means that it will be inherited via back propagation in the Simulink model. Back propagation may fail in certain circumstances; click Help for details.

-------------------- Step 7------------------

Set clock and reset parameters here. The time in these tables refers to time in the HDL simulator.

Please wait while generating waveforms.

...done

-------------------- Step 8------------------

The diagram below shows the current settings for forced 'Clock' and 'Reset' signals. The red line represents the time in the HDL simulation at which MATLAB/Simulink will start (i.e. cosimulation will start).

To change the MATLAB/Simulink start time relative to the HDL simulation time, enter the new start time below. To avoid a race condition, make sure the start time does not coincide with the active edge of any clock signal. You can do so by moving the start time or by changing the clock active edge in the previous step (click Back).

-------------------- Step 9------------------

When you click Finish, the Cosimulation Wizard performs the following actions:

- Creates and opens a new Simulink model containing an HDL Cosimulation block configured to your specifications.

- Generates the scripts to compile your HDL code and launch the HDL simulator according

to the choices you made with this assistant.

- (If you check the box below) Configures the HDL Cosimulation block to assist you in setting the timescale

when you cosimulate the block for the first time.

- (If you uncheck the box below) The timescale is set to the default setting of 1 Simulink second = 1 second in the HDL simulator

or you may change it below.

Generating blocks ... Please wait.

Warning: The model name 'hdlverifier_wizard_rcosflt_rtl' is shadowing another

name in the MATLAB workspace or path. Type "which -all

hdlverifier_wizard_rcosflt_rtl" at the command line to find the other uses of

this name. You should change the name of the model to avoid problems.

...done

The workflow executes the steps and generates a Simulink model named hdlverifier_wizard_rcosflt_rtl.slx, which includes an HDL Cosimulation block and two additional blocks for compilation and communication with the HDL simulator.

Open the provided testbench model.

open_system('rcosflt_tb.slx')

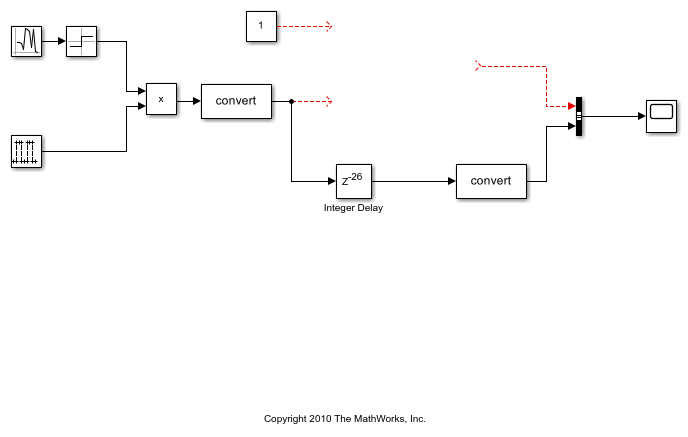

Drag the generated HDL Cosimulation block to the canvas, and connect its inputs and outputs to the testbench. Your model now looks similar to the following figure.

Run Cosimulation and Verify HDL Design

Start the HDL simulator by double-clicking the block labeled Launch HDL Simulator.

When the HDL simulator is ready, return to Simulink and start the simulation.

Determine timescale. Since the

AutoTimeScaleproperty is set to automatically determine the timescale at start of simulation, HDL Verifier launches the Timescale Details graphical interface instead of starting the simulation. Both the HDL simulator and Simulink sample thefilter_inandfilter_outports at 1 second. However, their sample time in the HDL simulator should be the same as the clock period (20 ns). Change the Simulink sample time of/rcosflt_rtl/clkto 1 (seconds), and press Enter. The wizard then updates the table. The following figure shows the new timescale: 1 second in Simulink corresponds to 2e-008 s in the HDL simulator.

4. Click OK to close the Timescale Details dialog box. Restart the Simulink simulation and verify the results from the scope in the testbench model.

The scope displays both the delayed version of input to the raised cosine filter and that filter's output. If you sample the output of this filter directly, no inter-symbol-interference occurs.

Limitations

The

.matfile that you generate in a MATLAB release is not guaranteed to work in other releases. For different MATLAB releases, regenerate the.matfile by running the Cosimulation Wizard workflow to completion using any customizations required for your design.

Version History

Introduced in R2022bSpecify or edit a parameter file to set values for HDL parameters. Use the

HDLParameterFile property to specify a parameter file.

When using the MATLAB System Object workflow, the default

data type for output ports is Fixedpoint Unsigned. In previous releases,

the default is Fixedpoint Signed.

Cosimulate with Synopsys® VCS and MATLAB.

Import a parameterized HDL design. Specify or edit a parameter file to set values for HDL parameters.

See Also

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)