Diese Seite wurde maschinell übersetzt.

Füllen Sie bitte eine 1-Minuten-Befragung zur Qualität dieser Übersetzung aus.

Eine produktive Reise zur Bereitstellung winziger neuronaler Netzwerke auf Mikrocontrollern

Von Danilo Pau, STMicroelectronics, und Brenda Zhuang, MathWorks

„Basierend auf MATLAB und Simulink Produkten sowie den Edge-KI-Tools von STMicroelectronics hilft das Framework Teams dabei, schnell Fachwissen im Bereich Deep Learning und Edge-Bereitstellung aufzubauen, sodass sie die üblichen Hürden bei tinyML überwinden können.“

Anwendungen für Machine Learning und Deep Learning werden zunehmend aus der Cloud auf Embedded-Geräte in der Nähe des Datenursprungs verlagert. Da der Edge-Computing-Markt schnell wächst, treiben mehrere Faktoren das Wachstum im Bereich Edge-KI voran, darunter Skalierbarkeit, steigende Nachfrage nach Echtzeit-KI-Anwendungen und die Verfügbarkeit kostengünstiger Edge-Geräte, ergänzt durch robuste und produktive Software-Toolchains. Darüber hinaus muss die Datenübertragung über ein Netzwerk vermieden werden – entweder aus Sicherheitsgründen oder einfach um die Kommunikationskosten zu minimieren.

Edge-KI umfasst eine breite Palette von Geräten, Sensoren, Mikrocontrollern, mehreren Mikroprozessoren auf einem Chip, Anwendungsprozessoren und dedizierten Systemen auf einem Chip – darunter auch relativ leistungsstarke Edge-Server und IoT-Module. Die Referenzgemeinschaft, die tinyML Foundation, gegründet im Jahr 2019, konzentriert sich auf die Entwicklung von Modellen für Machine Learning und deren Einsatz auf Embedded-Geräten mit extrem eingeschränkten Ressourcen, die über begrenzte Speicher-, Verarbeitungs- und Energieverbrauchsbudgets verfügen. tinyML eröffnet einzigartige Möglichkeiten, darunter Anwendungen, die mit kostengünstigen Batterien oder sogar kleinen Solarmodulen betrieben werden können, sowie groß angelegte Anwendungen, die Daten lokal auf kostengünstiger Hardware verarbeiten. Natürlich bringt tinyML auch verschiedene Herausforderungen mit sich. Eine solche Herausforderung besteht darin, dass Entwickler von Machine Learning und Embedded-Systemen die Leistung und den Platzbedarf einer Anwendung optimieren müssen, was Kenntnisse sowohl in KI als auch in Embedded-Systemen erfordert.

In diesem Kontext beschreibt dieser Artikel ein praktisches Framework für die Entwicklung und Bereitstellung tiefer neuronaler Netzwerke auf Edge-Geräten. Das Framework hilft den Teams, basierend auf MATLAB® und Simulink®-Produkten und STMicroelectronics® Edge-KI-Tools, schnell ihre Fachkompetenz im Bereich Deep Learning und Edge-Bereitstellung zu erweitern, sodass sie häufige Hürden bei tinyML überwinden können. Dies wiederum ermöglicht ihnen, schnell Prototypen von tinyML-Anwendungen zu erstellen und zu vergleichen. In den ersten Schritten des Workflows verwenden die Teams MATLAB, um ein Deep-Learning-Netzwerk aufzubauen, Hyperparameter mit Bayesscher Optimierung abzustimmen, Wissensdestillation zu verwenden und das Netzwerk mit Pruning und Quantisierung zu komprimieren. Im letzten Schritt nutzen die Entwickler ST Edge AI Core Technology, die in die ST Edge AI Developer Cloud – einen kostenlosen Onlinedienst zur Entwicklung von KI auf 32-Bit-Mikrocontrollern und Mikroprozessoren (STM32, Stellar) von STMicroelectronics, einschließlich Sensoren mit integrierter KI – integriert ist, zum Benchmarking der Ressourcennutzung und Inferenzgeschwindigkeit für das bereitgestellte Deep-Learning-Netzwerk (Abbildung 1).

Netzwerkdesign, Training und Hyperparameteroptimierung

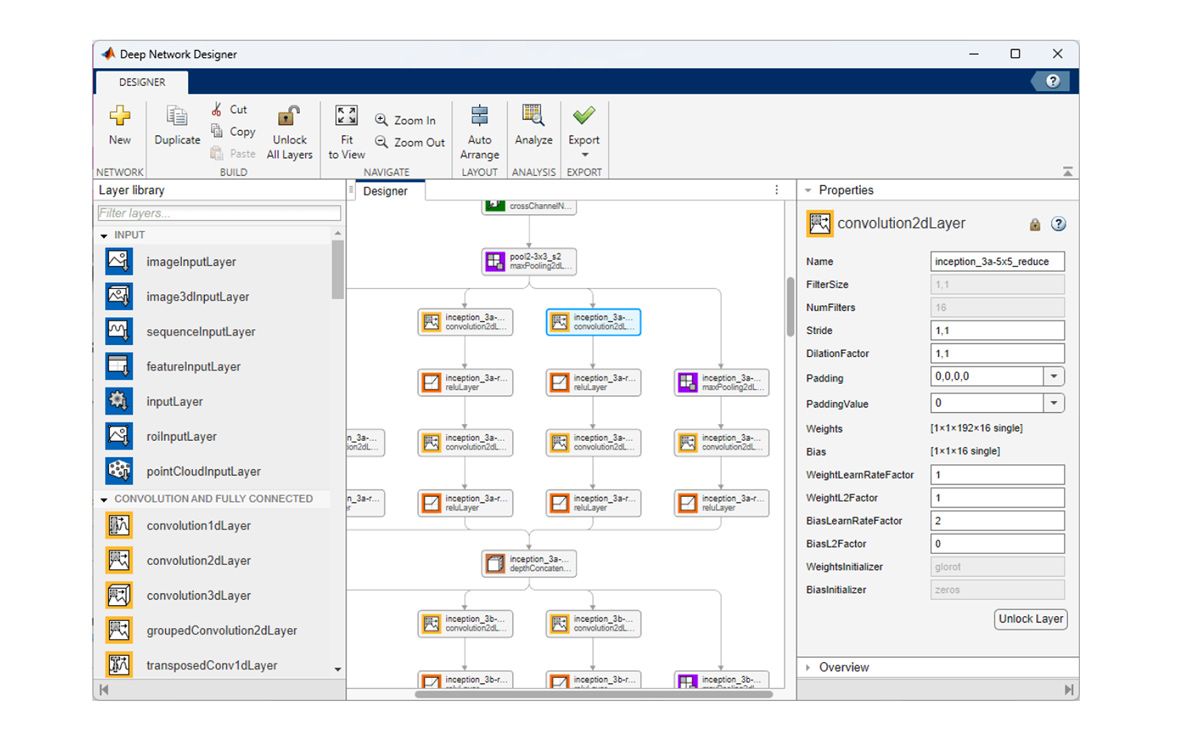

Sobald die Ingenieure den Datensatz für die Verwendung in der Deep-Learning-Anwendung gesammelt, vorverarbeitet und vorbereitet haben, besteht der nächste Schritt darin, Kandidatenmodelle zu trainieren und zu bewerten. Dazu können gehören: vorab trainierte Modelle, wie NASNet, SqueezeNet, Inception-v3 und ResNet-101 oder Modelle, die der Machine-Learning-Ingenieur interaktiv erstellt hat, mithilfe der Deep Network Designer-App (Abbildung 2). Mehrere Modelle bieten Beispiele, die zur Beschleunigung der Entwicklung verwendet werden können, darunter Beispielmodelle für Bild, Video, Klang und Lidar; Punktwolkenklassifizierung; Objekterkennung; Posenschätzung und Wellenformsegmentierung.

Die Leistung eines Deep-Learning-Netzwerks hängt stark sowohl von den Parametern ab, die sein Training bestimmen, als auch von denen, die seine Netzwerkarchitektur beschreiben. Beispiele dieser Hyperparameter sind Lernrate und Batchgröße, die Anzahl und Art der Schichten sowie die Verbindungen zwischen den Schichten. Durch die richtige Abstimmung der Hyperparameter können Modelle entstehen, die eine höhere Genauigkeit und bessere Leistung erzielen, selbst in den ressourcenbeschränkten Umgebungen, in denen tinyML-Anwendungen ausgeführt werden. Das Auswählen und Feinabstimmen von Hyperparameterwerten, um die leistungsoptimierende Kombination zu finden, kann jedoch eine schwierige und zeitaufwändige Aufgabe sein.

Die Bayessche Optimierung eignet sich gut für die Hyperparameteroptimierung von Deep-Learning-Netzwerken für Klassifizierung und Regression, da sie den hochdimensionalen Hyperparameterraum effizient erkundet, um optimale oder nahezu optimale Konfigurationen zu finden. In MATLAB kann der Entwickler von Machine Learning die bayesopt-Funktion zum Finden der besten Hyperparameterwerte mithilfe der Bayesschen Optimierung nutzen. Beispielsweise kann es einen Satz von Hyperparametern zur Auswertung bereitstellen – etwa die Anzahl der Faltungsschichten, die anfängliche Lernrate, den Impuls und die L2-Regularisierung – sowie eine Zielfunktion, etwa den Validierungsfehler, der minimiert werden soll. Die Funktion kann dann die Ergebnisse von bayesopt nutzen, um einen oder mehrere Sätze von Hyperparameterkonfigurationen auszuwählen, die in den nächsten Phasen des Workflows genauer untersucht werden sollen.

Wissensdestillation

Ressourcenbeschränkte Embedded-Geräte haben nur begrenzten Speicher zur Verfügung. Wissensdestillation ist ein Ansatz, um den Platzbedarf eines Deep-Learning-Netzwerks zu reduzieren und gleichzeitig ein hohes Maß an Genauigkeit beizubehalten. Bei dieser Technik wird ein größeres und genaueres Lehrernetzwerk verwendet, um einem kleineren Schülernetzwerk das Treffen von Vorhersagen beizubringen. Der Schlüssel liegt in der Auswahl von Verlustfunktionen in den Lehrer-Schüler-Netzwerkarchitekturen.

Als Lehrermodell können die in den früheren Schritten trainierten Netzwerke verwendet werden. Ein Schülernetzwerk ist eine kleinere, aber ähnliche Version des Lehrermodells. Normalerweise enthält das Schülermodell weniger Convolution-Batchnorm-ReLU-Blöcke. Um der Dimensionsreduzierung Rechnung zu tragen, werden im Schülernetzwerk Max-Pooling-Schichten oder Global Average Pooling hinzugefügt. Durch diese Modifikationen wird die Anzahl der Lerninhalte im Vergleich zum Lehrernetzwerk deutlich reduziert.

Zum Trainieren des Schülernetzwerks muss eine Verlustfunktion zur Wissensdestillation definiert werden. Sie wird aus den Eingaben des Schülernetzwerks, des Lehrernetzwerks, Eingabedaten mit einem entsprechenden Ziel und dem Temperatur-Hyperparameter bestimmt. Empirisch besteht die Verlustfunktion aus einem gewichteten Durchschnitt von 1) dem harten Verlust, also dem Kreuzentropieverlust zwischen den Ausgaben des Schülernetzwerks und dem wahren Label, und 2) dem weichen Verlust, also dem Kreuzentropieverlust des SoftMax mit Temperatur zwischen den Logits des Schülernetzwerks und denen des Lehrernetzwerks.

Das trainierte Schülernetzwerk bewahrt die Genauigkeit des Lehrernetzwerks besser und erreicht eine Reduzierung der lernbaren Parameter, wodurch es sich besser für den Einsatz auf Embedded-Geräten eignet.

Modellkomprimierung und -optimierung

Ein effizienter Entwurf und die Optimierung der Hyperparameter während der Trainingsphase sind ein wichtiger erster Schritt. Sie reichen jedoch nicht aus, um die Bereitstellung auf Edge-Geräten zu gewährleisten. Daher ist eine Optimierung nach dem Training durch Modellbeschneidung und -quantisierung wichtig, um den Speicherbedarf und die Rechenleistungsanforderungen eines tiefen neuronalen Netzwerks weiter zu reduzieren.

Eine der effektivsten Methoden der Netzwerkkomprimierung ist die Quantisierung. Dies liegt daran, dass die Daten mit ganzzahliger Genauigkeit erfasst werden, da keine Sensoren mit großem Volumen Gleitkommadarstellungen ausgeben. Ziel der Quantisierung ist es, den zum Speichern der Netzwerkparameter erforderlichen Speicherbedarf zu reduzieren und die Rechengeschwindigkeit zu erhöhen, indem die Gewichte und Aktivierungen des Modells mit einer reduzierten Anzahl von Bits dargestellt werden. Dies kann beispielsweise das Ersetzen von 32-Bit-Gleitkommazahlen durch 8-Bit-Ganzzahlen beinhalten – auch hier gilt, dass dies nur unter Inkaufnahme einer marginalen Verschlechterung der Vorhersagegenauigkeit möglich ist. Durch die Quantisierung ist eine sparsame Nutzung des Embedded Memory möglich, was für ressourcenbeschränkte Sensoren, Mikrocontroller und Mikroprozessoren (Abbildung 3) am Edge von entscheidender Bedeutung ist. Darüber hinaus sind Ganzzahloperationen auf Hardware im Allgemeinen schneller als Gleitkommaoperationen, was zu einer Verbesserung der Inferenzleistung auf Mikrocontrollern führt. Dies führt dazu, dass die Modelle weniger Strom verbrauchen und sich daher noch besser für den Einsatz auf batteriebetriebenen oder energiebeschränkten Geräten wie Mobiltelefonen und IoT-Geräten eignen. Während die Quantisierung nach dem Training zu gewissen Genauigkeitsverlusten führen soll, sind die Quantisierungstools in MATLAB darauf ausgelegt, die Auswirkungen auf die Modellgenauigkeit zu minimieren. Um die Leistung des quantisierten Modells aufrechtzuerhalten, werden Techniken wie Feinabstimmung und Kalibrierung verwendet. In MATLAB vereinfacht die dlquantizer-Funktion den Prozess der Quantisierung der Gewichte, Biase und Aktivierungen eines tiefen neuronalen Netzwerks auf 8-Bit-Ganzzahlwerte.

Im Gegensatz dazu konzentrieren sich Bereinigungstechniken darauf, die Komplexität eines Netzwerks durch Minimierung der Betriebsredundanz zu reduzieren. Dies ist von grundlegender Bedeutung, um die Rechenkomplexität drastisch zu reduzieren. Die Idee besteht darin, diejenigen Verbindungen, Gewichte, Filter oder sogar ganze Schichten zu identifizieren und zu entfernen, die wenig Einfluss auf die Vorhersagen des Netzwerks haben. Projektion ist eine proprietäre MATLAB Technik zur Optimierung neuronaler Netzwerke durch selektives Entfernen weniger wichtiger Gewichte oder Verbindungen. Dieser Prozess reduziert die Komplexität des Modells, was zu einer kleineren Modellgröße und schnelleren Inferenzzeiten führt, ohne die Leistung wesentlich zu beeinträchtigen. Während beim regulären Beschneiden im Allgemeinen eine einfache, schwellenwertbasierte Entfernung von Gewichten geringer Größenordnung erfolgt, können bei der Projektion komplexere Kriterien und Methoden zum Einsatz kommen, um sicherzustellen, dass die wesentlichen Merkmale des Netzwerks erhalten bleiben. Darüber hinaus zielt die Projektion häufig darauf ab, die geometrischen Eigenschaften des Gewichtsraums beizubehalten, was im Vergleich zu herkömmlichen Beschneidungsmethoden zu potenziell effizienteren und robusteren Modellen führt.

Benchmarking in der ST Edge AI Developer Cloud

Nach Abschluss des anfänglichen Netzwerkentwurfs, der Hyperparameteroptimierung, der Destillation und der Komprimierung in MATLAB besteht der nächste Schritt im Arbeitsablauf darin, die Leistung dieses Entwurfs auf einem Mikrocontroller oder Mikroprozessor zu bewerten. Insbesondere müssen Ingenieure unter anderem die Flash- und RAM-Anforderungen des Netzwerks sowie die Inferenzgeschwindigkeit bewerten.

ST Edge AI Developer Cloud wurde entwickelt, um diese Phase des Workflows zu optimieren, indem es ein schnelles Benchmarking von Netzwerken auf ST Edge-Geräten ermöglicht. Um diesen Dienst für eine in MATLAB entwickelte tinyML-Anwendung zu verwenden, müssen Sie zunächst das Netzwerk in das ONNX-Format exportieren. Nachdem die generierte ONNX-Datei in die ST Edge AI Developer Cloud hochgeladen wurde, können die Ingenieure das oder die ST-Geräte auswählen, auf denen die Benchmarks ausgeführt werden sollen (Abbildung 4).

Sobald das Benchmarking abgeschlossen ist, stellt ST Edge AI Developer Cloud einen Bericht mit detaillierten Ergebnissen bereit (Abbildung 5). Die von der ST Edge AI Developer Cloud bereitgestellten Tools zur Leistungsanalyse bieten eine Vielzahl detaillierter Einblicke, darunter in Speichernutzung, Verarbeitungsgeschwindigkeit, Ressourcennutzung und Modellgenauigkeit. Entwickler erhalten Informationen zum RAM- und Flash-Speicherverbrauch sowie eine Aufschlüsselung der Speicherzuweisung für verschiedene Ebenen und Komponenten des Modells. Darüber hinaus liefern die Tools Angaben zur Ausführungszeit jeder Ebene und zur gesamten Inferenzzeit sowie eine detaillierte Zeitanalyse, um langsame Vorgänge zu identifizieren und zu optimieren. Statistiken zur Ressourcennutzung, einschließlich der CPU- und Hardwarebeschleunigernutzung sowie Kennzahlen zum Stromverbrauch helfen bei der Optimierung der Energieeffizienz.

Nach der Überprüfung der Benchmark-Ergebnisse können die Ingenieure die optimale Vorgehensweise für die nächsten Schritte ermitteln. Wenn das Netzwerkdesign problemlos in die Beschränkungen eines bestimmten Edge-Geräts mit kurzen Inferenzzeiten passt, können Sie Möglichkeiten prüfen, entweder ein kleineres Gerät zu verwenden oder die Vorhersagegenauigkeit mit einem etwas größeren, komplexeren Netzwerk zu verbessern. Wenn andererseits das Netzwerkdesign zu groß ist und die Inferenzzeiten aufgrund der Verwendung von externem Flash oder RAM langsam sind, sucht das Team möglicherweise nach einem Gerät mit mehr Rechenleistung und mehr Embedded Flash und RAM oder führt zusätzliche Hyperparameteroptimierungen, Wissensdestillationen, Bereinigungen und Quantisierungsiterationen mit MATLAB durch, um das Netzwerk weiter zu komprimieren. Die ST Edge AI Developer Cloud bietet außerdem eine automatische Codegenerierung, um die Bereitstellung von KI-Modellen auf ST-Geräten zu optimieren. Diese Funktion konvertiert trainierte KI-Modelle in optimierten C-Code, der mit den Sensoren, Mikrocontrollern und Mikroprozessoren von STMicroelectronics kompatibel ist.

Vom Benchmarking bis zur Bereitstellung

Der letzte Schritt im Workflow ist die Bereitstellung auf einem Sensor, Mikrocontroller oder Mikroprozessor. Mit den Benchmarking-Ergebnissen können die Ingenieure eine fundierte Entscheidung über die Auswahl einer Plattform treffen, wie zum Beispiel ein STM32 Discovery Kit, etwa zur Evaluierung ihrer tinyML-Anwendung auf echter Hardware.

Je nach Anwendung müssen sie das tiefe neuronale Netzwerk möglicherweise mit anderen Komponenten, etwa einem Controller, integrieren und diese vor der Bereitstellung in ein größeres System einbinden. Für diese Anwendungsfälle können sie den Workflow weiter ausbauen, indem sie die anderen Komponenten in Simulink modellieren, Simulationen auf Systemebene ausführen, um das Design zu validieren, und C/C++ Code für die Bereitstellung auf STM32-Geräten mit Embedded Coder® und Embedded Coder-Unterstützung für STM32 zu generieren.

Veröffentlicht 2024